**TECHNICAL MANUAL**

ORGANIZATIONAL MAINTENANCE MANUAL MAGNETIC TAPE UNIT

> EXPANDED TROUBLESHOOTING (LOGIC DIAGRAM THEORY)

> > GUIDED MISSILE AIR DEFENSE SYSTEM AN/TSQ-73

## WARNING

## DANGEROUS VOLTAGE

#### is used in the operation of this equipment

#### **DEATH ON CONTACT**

#### may result if personnel fail to observe safety precautions

Never work on electronic equipment unless there is another person nearby who is familiar with the operation and hazards of the equipment and who is competent in administering first aid. When the technician is aided by operators, he must warn them about dangerous areas.

Whenever possible, the power supply to the equipment must be shut off before beginning work on the equipment. Take particular care to ground every capacitor likely to hold a dangerous potential. When working inside the equipment, after the power has been turned off, always ground every part before touching it.

Be careful not to contact high-voltage connections when installing or operating this equipment.

Whenever the nature of the operation permits, keep one hand away from the equipment to reduce the hazard of current flowing through vital organs of the body.

#### WARNING

Do not be misled by the term "low voltage." Potentials as low as 50 volts may cause death under adverse conditions.

# **EXTREMELY DANGEROUS POTENTIALS**

greater than 500 volts exist in the following units: Display console high voltage power supply Display console CRT

#### WARNING

For emergencies requiring immediate shutdown of system power, press SYSTEM POWER OFF switch located on power cabinet power transfer unit. Observe that SYSTEM POWER ON indicator light goes off.

a/(b blank)

# LIST OF EFFECTIVE PAGES

Insert latest changes page, dispose of superseded pages in accordance with applicable regulations.

# NOTE:

# On a changed page, the portion of the text affected by the latest change is indicated by a vertical line in the margin of the page.

Dates of issue for original and change pages are:

Original ......0...... 5 Jun 84

| Page<br>No.   | *Change<br>No. | Page<br>No.   | *Change<br>No. | Page<br>No.   | *Change<br>No. |

|---------------|----------------|---------------|----------------|---------------|----------------|

| а             | •              | 5-122 blank   | 0              | 5-177         |                |

| b blank       | 0              | 5-123 - 5-126 |                | 5-178 blank   |                |

| Α             | •              | 5-127         | 0              | 5-179 - 5-182 | 0              |

| B blank       |                | 5-128 blank   |                | 5-183         |                |

| i - v         | 0              | 5-129 - 5-130 |                | 5-184 blank   | 0              |

| vi blank      |                | 5-131         |                | 5-185         |                |

| 5-1 - 5-84    |                | 5-132 blank   |                | 5-186 blank   | 0              |

| 5-85          |                | 5-133         |                | 5-187         | -              |

| 5-86 blank    | 0              | 5-134 blank   | 0              | 5-188 blank   | 0              |

| 5-87          | 0              | 5-135 - 5-146 | 0              | 5-189         | 0              |

| 5-88 blank    | 0              | 5-147         | 0              | 5-190 blank   | 0              |

| 5-89 - 5-94   | 0              | 5-148 blank   | 0              | 5-191         | 0              |

| 5-95          | 0              | 5-149         | 0              | 5-192 blank   | 0              |

| 5-96 blank    | 0              | 5-150 blank   | 0              | 5-193 - 5-198 | 0              |

| 5-97          | 0              | 5-151 - 5-152 | 0              | 5-199         | 0              |

| 5-98 blank    | 0              | 5-153         | 0              | 5-200 blank   | 0              |

| 5-99          | 0              | 5-154 blank   | 0              | 5-201 - 5-202 | 0              |

| 5-100 blank   | 0              | 5-155         | 0              | 5-203         | 0              |

| 5-101 - 5-102 | 0              | 5-156 blank   | 0              | 5-204 blank   | 0              |

| 5-103         | 0              | 5-157 - 5-158 | 0              | 5-205         | 0              |

| 5-104 blank   | 0              | 5-159         | 0              | 5-206 blank   | 0              |

| 5-105         | 0              | 5-160 blank   | 0              | 5-207 - 5-208 | 0              |

| 5-106 blank   | 0              | 5-161         | 0              | 5-209         | 0              |

| 5-107 - 5-108 | 0              | 5-162 blank   | 0              | 5-210 blank   | 0              |

| 5-109         | 0              | 5-163 -5-164  |                | 5-211 - 5-212 | 0              |

| 5-110 blank   | 0              | 5-165         | 0              | 5-213         | 0              |

| 5-111         | 0              | 5-166 blank   | 0              | 5-214 blank   | 0              |

| 5-112 blank   | 0              | 5-167         | 0              | 5-215 - 5-216 | 0              |

| 5-113         | 0              | 5-168 blank   | 0              | 5-217         | 0              |

| 5-114 blank   | 0              | 5-169 - 5-170 | 0              | 5-218 blank   | 0              |

| 5-115 - 5-116 | 0              | 5-171         | 0              | 5-219         | 0              |

| 5-117         |                | 5-172 blank   |                | 5-220 blank   |                |

| 5-118 blank   | -              | 5-173         |                | 5-221 - 5-222 | 0              |

| 5-119         |                | 5-174 blank   |                | 5-223         |                |

| 5-120 blank   |                | 5-175 - 5-176 |                | 5-224 blank   |                |

| 5-121         |                |               | -              |               | -              |

\*Zero in this column indicates an original page.

TECHNICAL MANUAL

)

)

No. 9-1430-655-20-5-2

HEADQUARTERS DEPARTMENT OF THE ARMY Washington, D.C., 5 June 1984

## ORGANIZATIONAL MAINTENANCE MANUAL: MAGNETIC TAPE UNIT EXPANDED TROUBLESHOOTING (LOGIC DIAGRAM THEORY) GUIDED MISSILE AIR DEFENSE SYSTEM AN/TSQ-73

## **REPORTING OF ERRORS**

You can help improve this publication. If you find any mistakes, or if you know of a way to improve the procedures, please let us know. Mail your letter, DA Form 2028 (Recommended Changes to Publications and Blank Forms), or DA Form 2028-2 located in back of this manual direct to: Commander, U.S. Army Missile Command, ATTN: DRSMI-SNPM, Redstone Arsenal, AL 35898. A reply will be furnished to you.

## TABLE OF CONTENTS

| Chapter |                                                                            |                                                                                                                                                                                                                                                                  | Page                                                               |  |  |  |

|---------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--|--|--|

|         |                                                                            | ATIONS                                                                                                                                                                                                                                                           | iii<br>v                                                           |  |  |  |

| 5       |                                                                            | MAGNETIC TEST SET EXPANDED TROUBLESHOOTING                                                                                                                                                                                                                       |                                                                    |  |  |  |

|         | Sectio                                                                     | Section I. INTRODUCTION                                                                                                                                                                                                                                          |                                                                    |  |  |  |

|         | 5-1.<br>5-2.<br>5-3.<br>5-4.<br>5-5.<br>Key S                              | Scope<br>Expanded Troubleshooting Concept<br>Troubleshooting Aids<br>Physical Description<br>Circuit Card Location Index Tables and<br>ignal Lookup Tables                                                                                                       | 5-1<br>5-1<br>5-1                                                  |  |  |  |

|         | Sectio                                                                     | on II. OVERALL THEORY OF OPERATION                                                                                                                                                                                                                               |                                                                    |  |  |  |

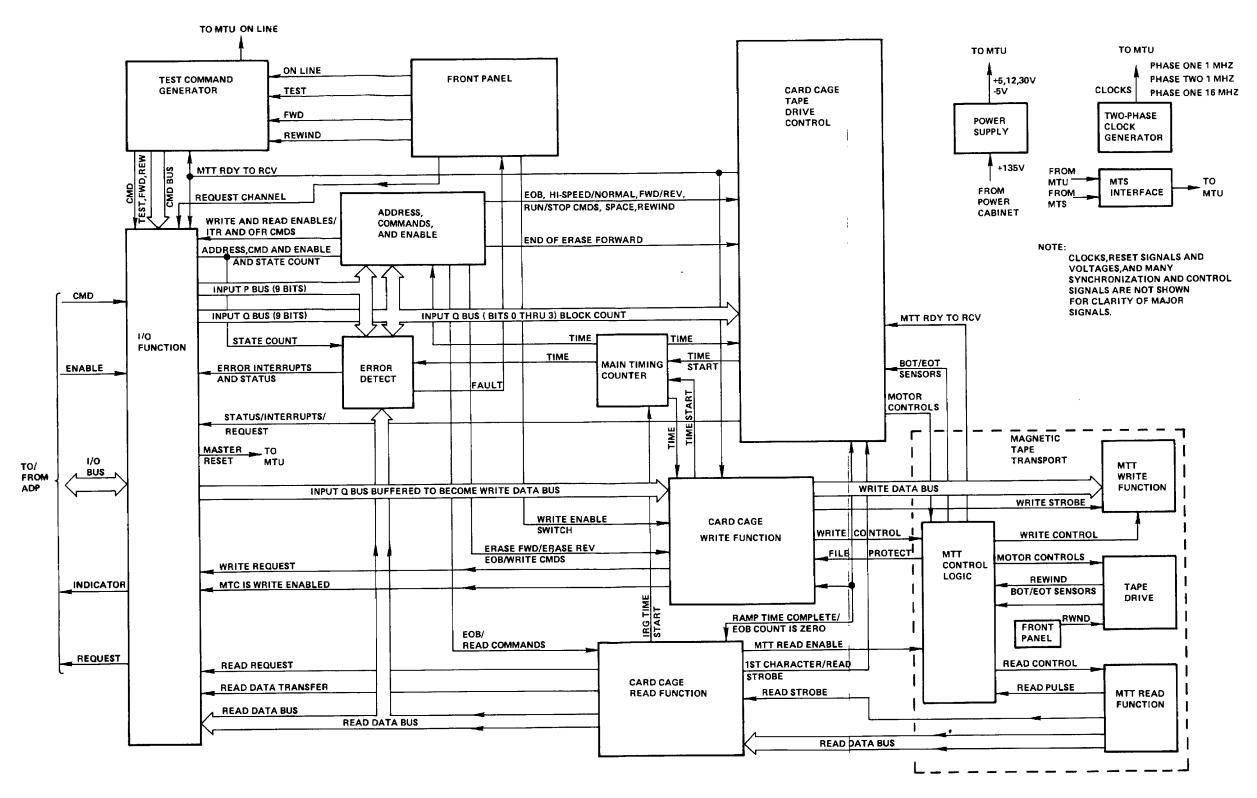

|         | 5-6.                                                                       | Overall Functional Description                                                                                                                                                                                                                                   | 5-83                                                               |  |  |  |

|         | Sectio                                                                     | on III. DETAILED DESCRIPTION                                                                                                                                                                                                                                     |                                                                    |  |  |  |

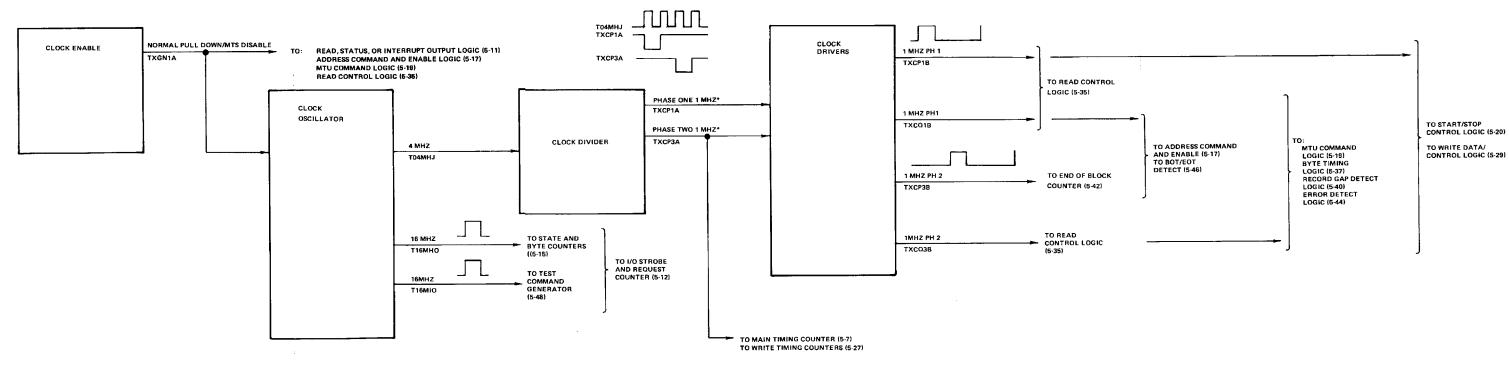

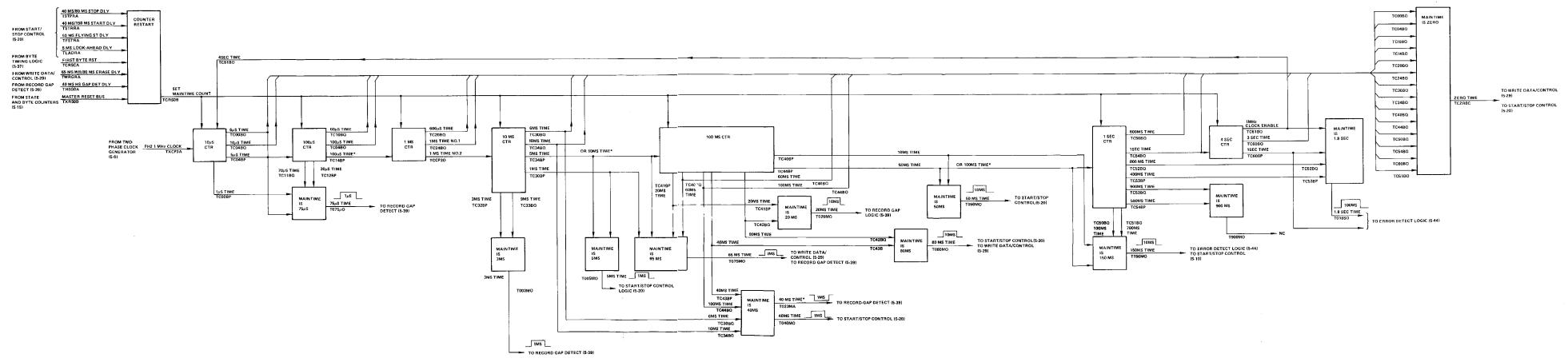

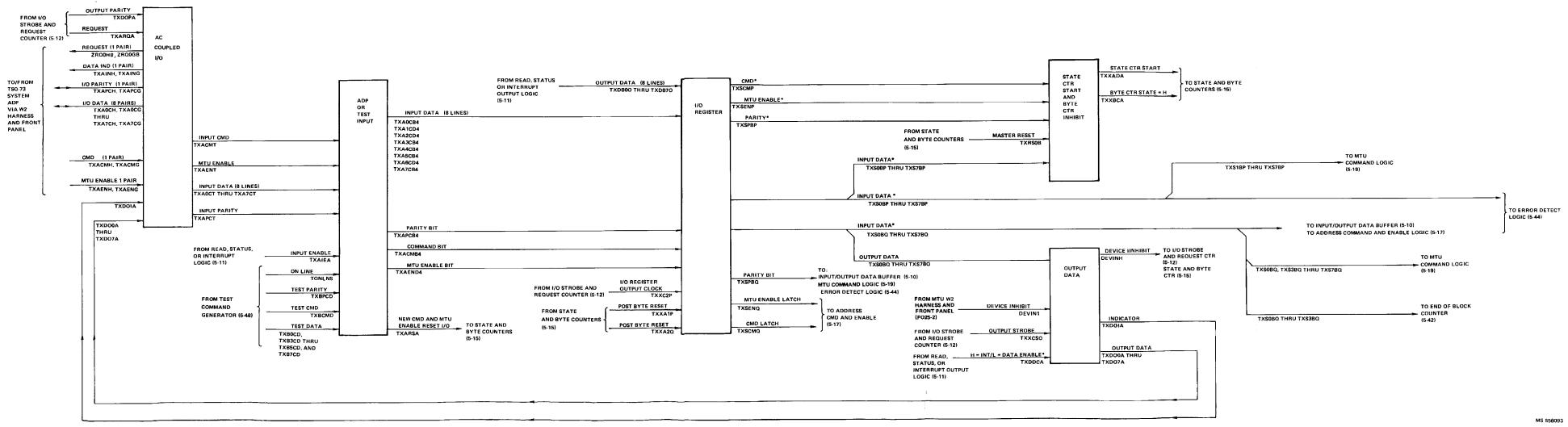

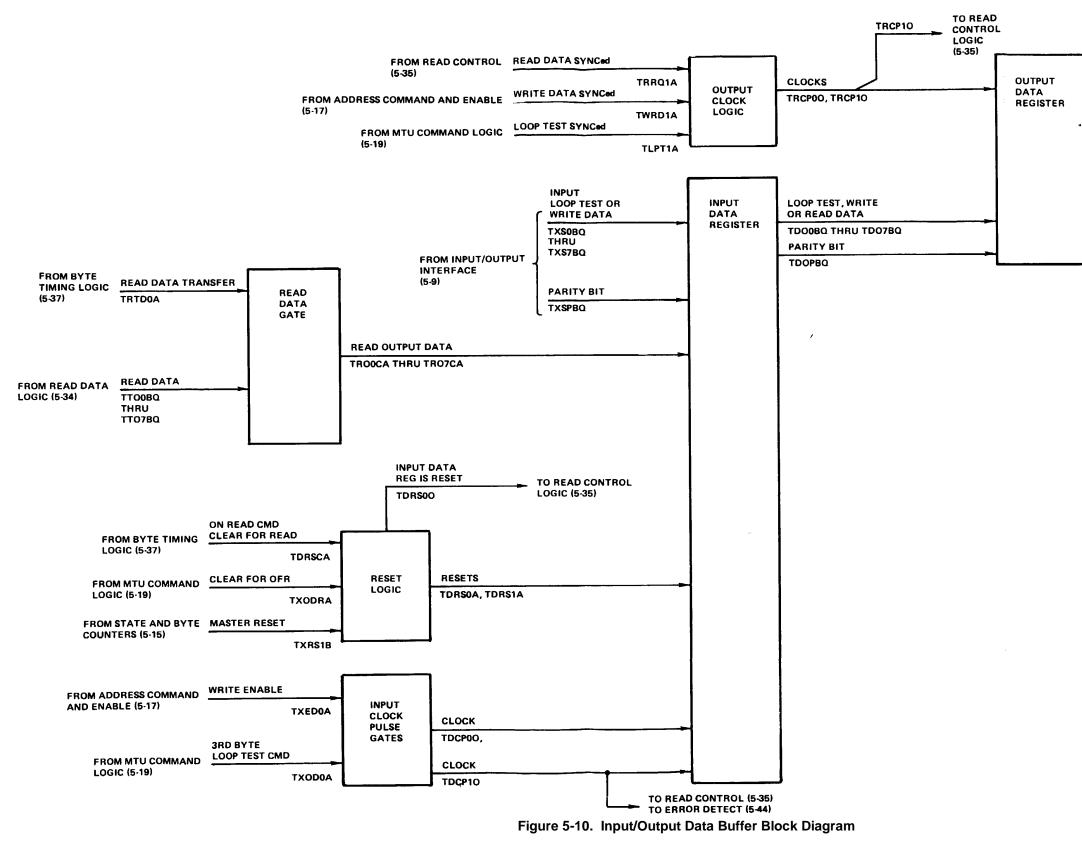

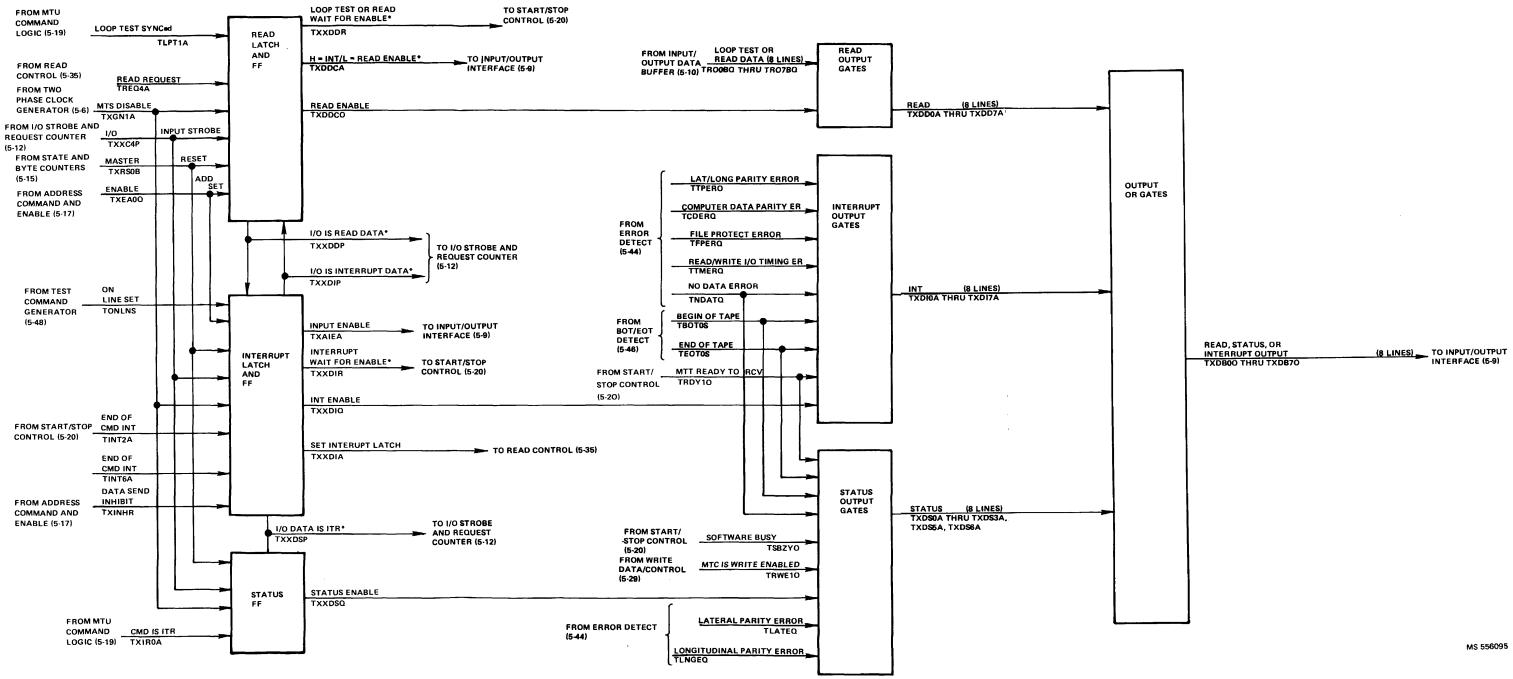

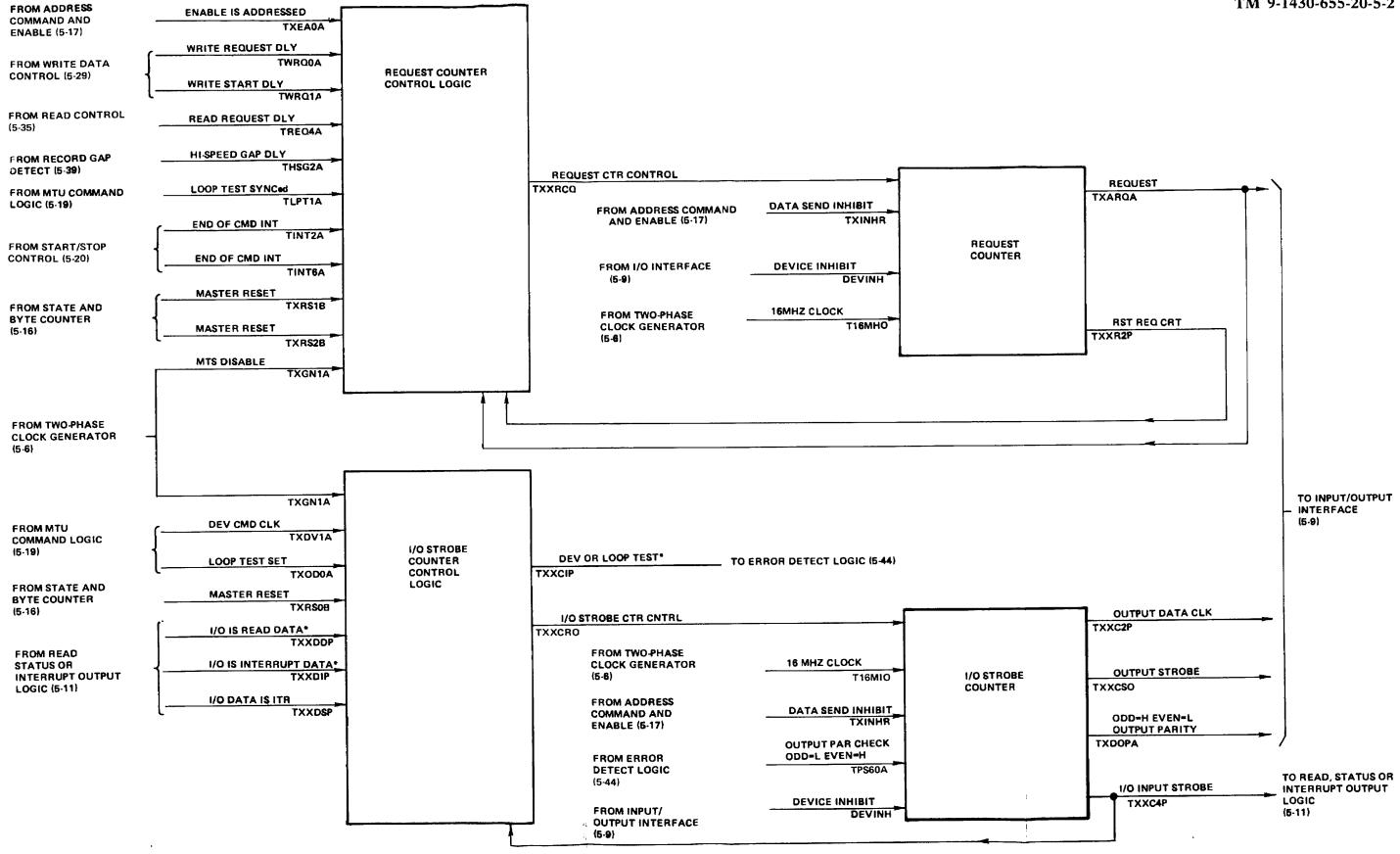

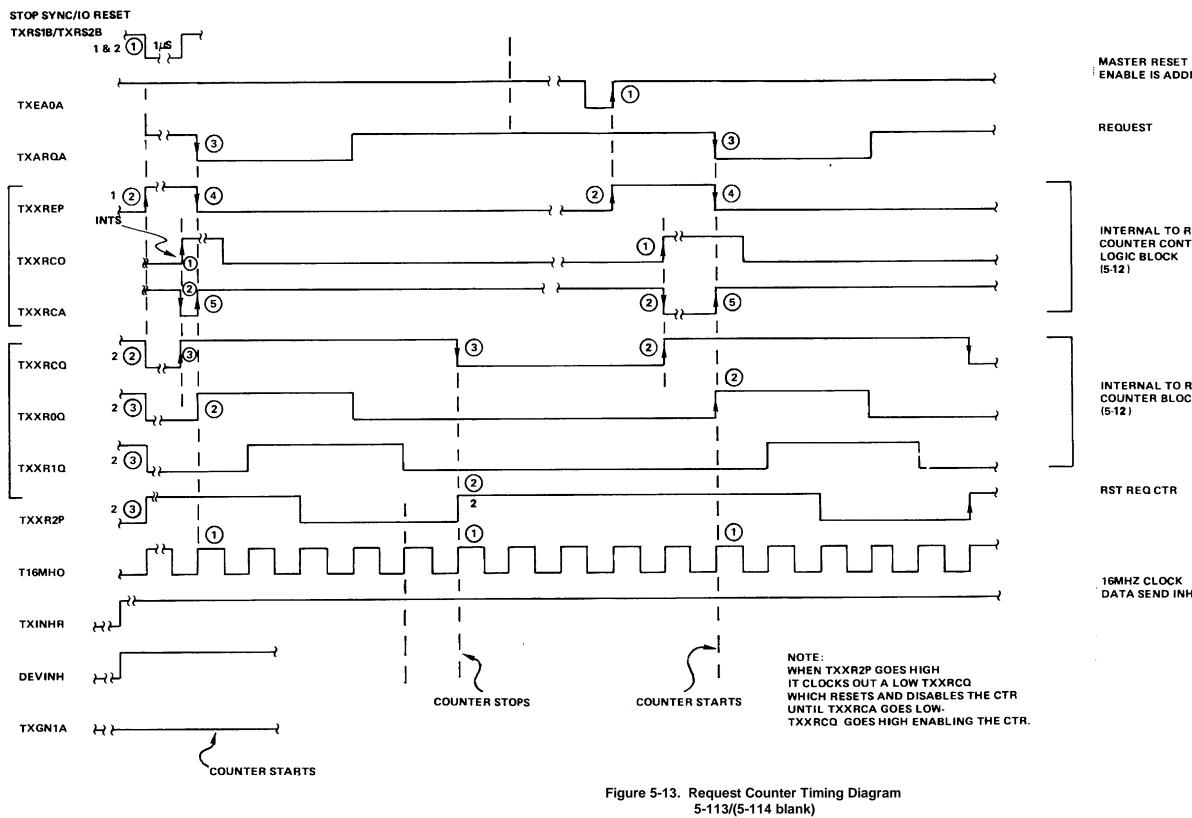

|         | 5-7.<br>5-8.<br>5-9.<br>5-10.<br>5-11.<br>5-12.<br>5-13.<br>5-14.<br>5-15. | General<br>Two-Phase Clock Generator<br>Main Timing Counter<br>Input/Output Interface<br>Input/Output Data Buffer<br>Read, Status, or Interrupt Output Logic<br>I/O Strobe and Request Counters<br>State and Byte Counters<br>Address, Command, and Enable Logic | 5-93<br>5-94<br>5-101<br>5-102<br>5-107<br>5-108<br>5-116<br>5-116 |  |  |  |

|         | 5-16.<br>5-17.                                                             | MTU Commands Logic                                                                                                                                                                                                                                               | 5-124                                                              |  |  |  |

# **TABLE OF CONTENTS - Continued**

# Chapter

# Page

| 5-18. | Write Timing Counter                    |       |

|-------|-----------------------------------------|-------|

| 5-19. | Write Data Control Logic                | 5-151 |

| 5-20. | Read Data Logic                         | 5-164 |

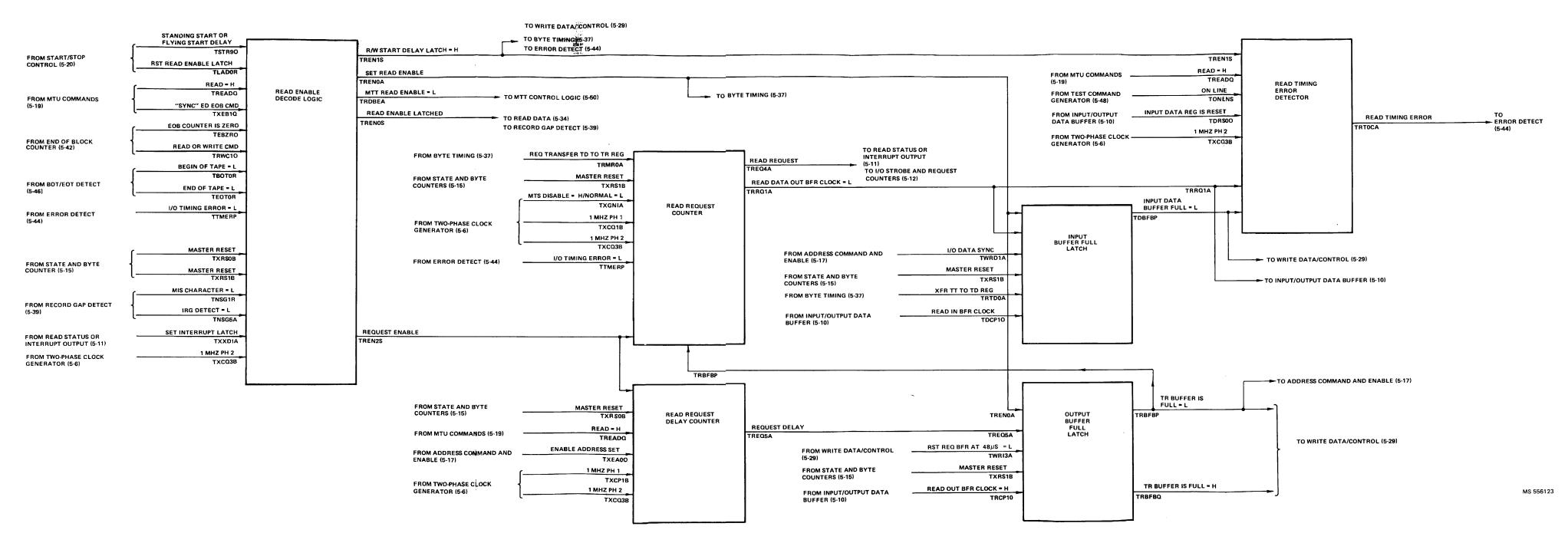

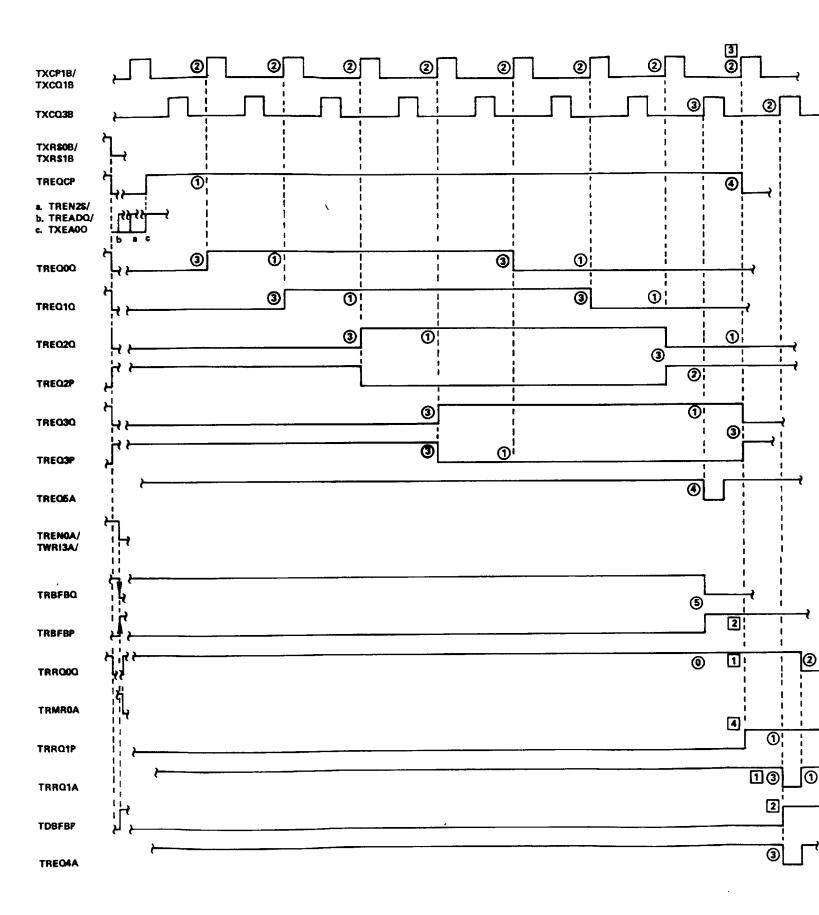

| 5-21. | Read Control Logic                      | 5-164 |

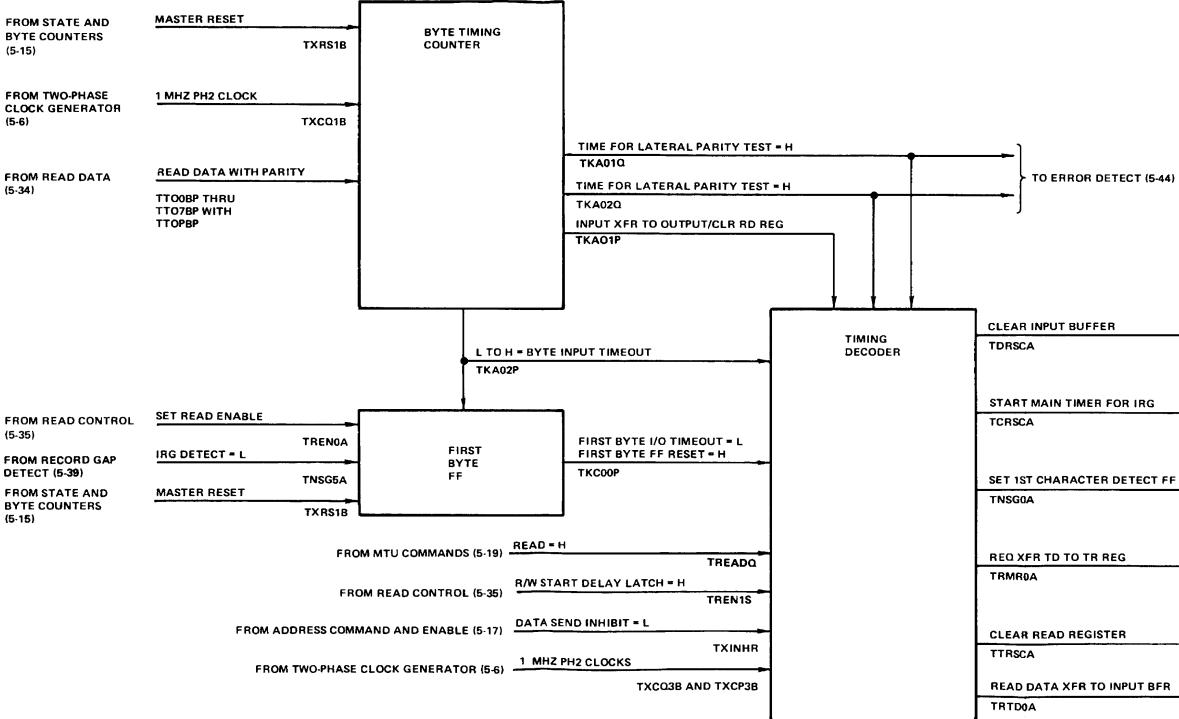

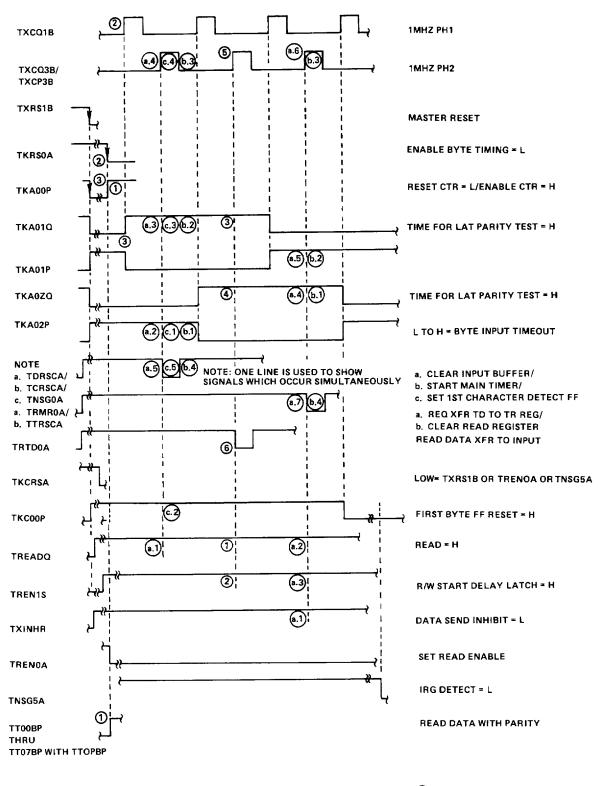

| 5-22. | Byte Timing Logic                       | 5-170 |

| 5-23. | Record Gap Detect Logic                 | 5-176 |

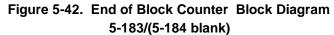

| 5-24. | End of Block (EOB) Counter              | 5-180 |

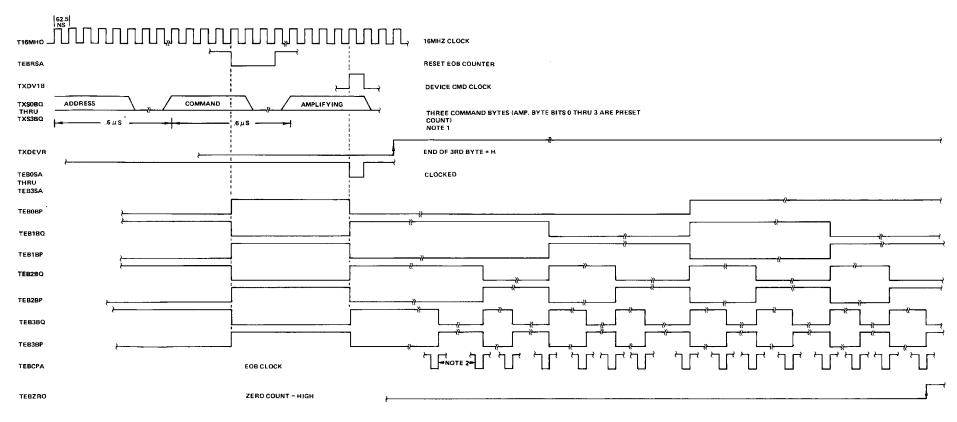

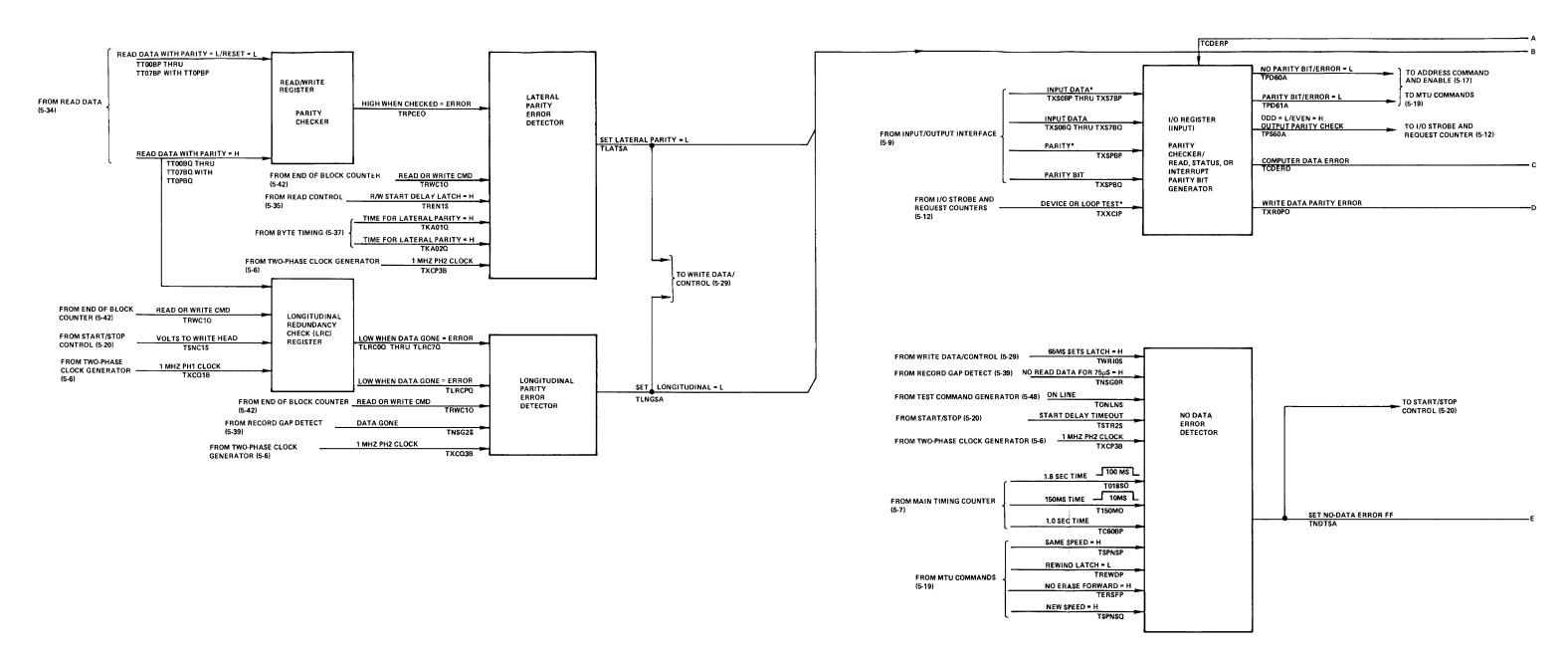

| 5-25. | Error Detect Logic                      | 5-182 |

| 5-26. | Beginning of Tape/End of Tape (BOT/EOT) |       |

|       | Detect Logic                            | 5-196 |

| 5-27. | Test Command Generator                  | 5-198 |

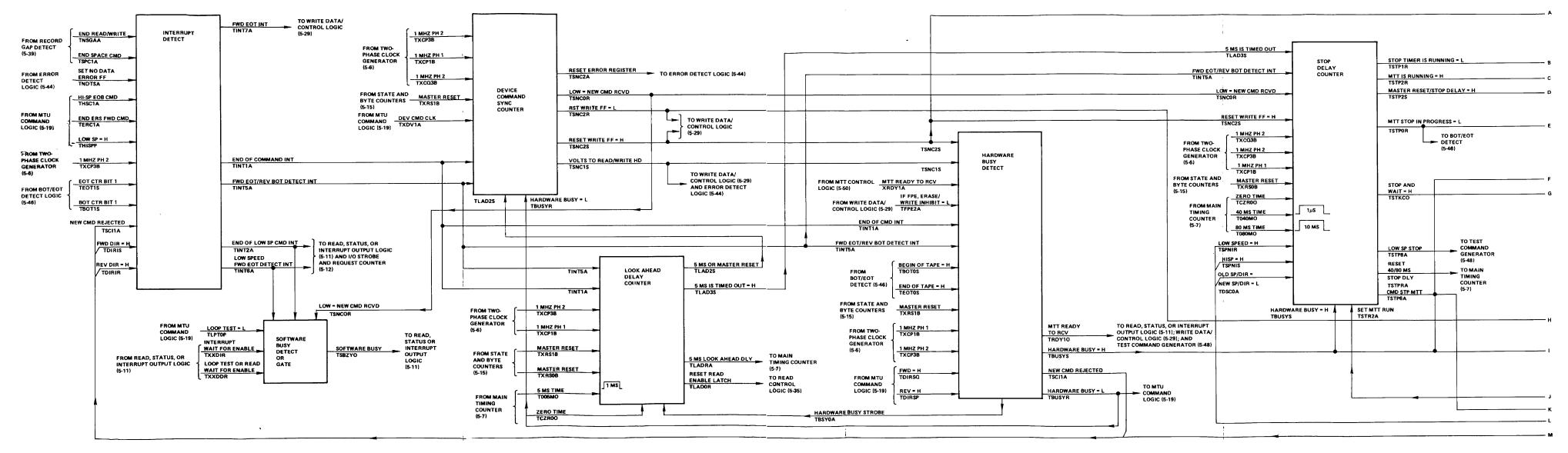

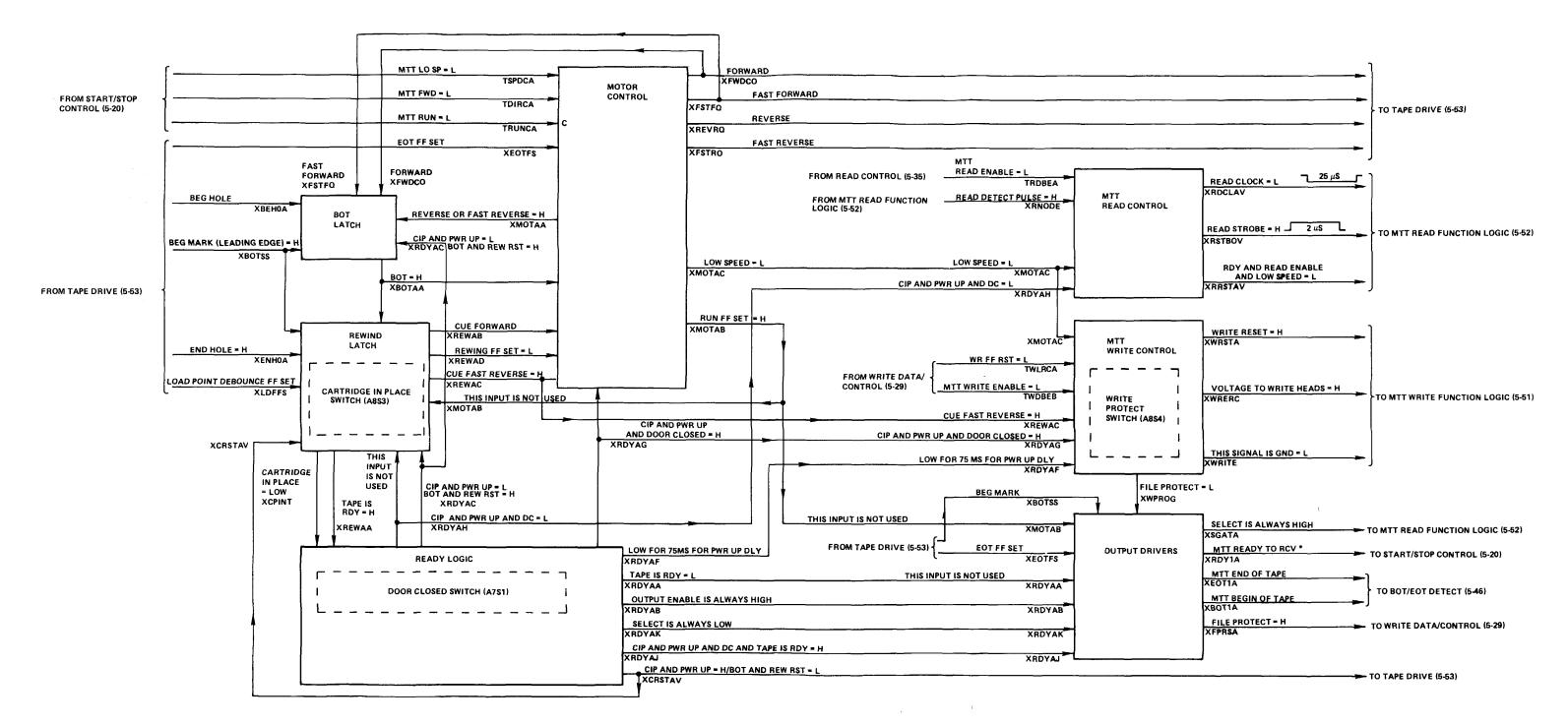

| 5-28. | MTT Control Logic                       | 5-207 |

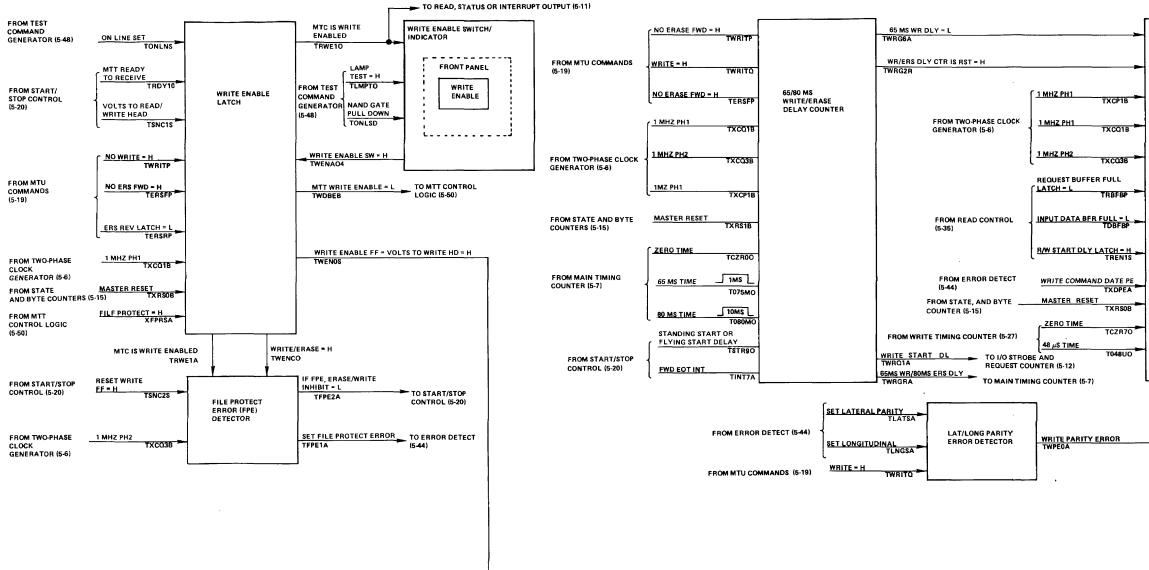

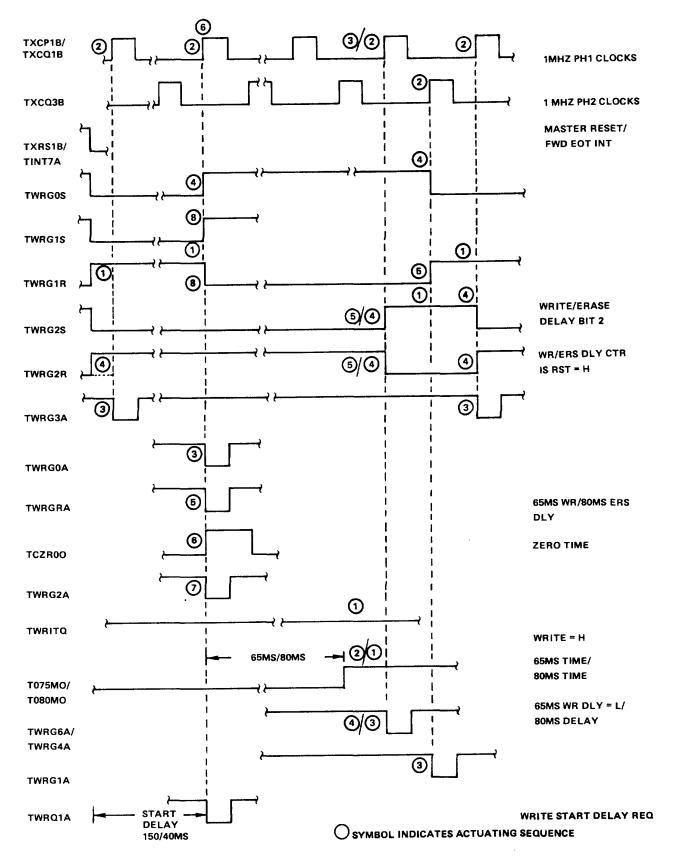

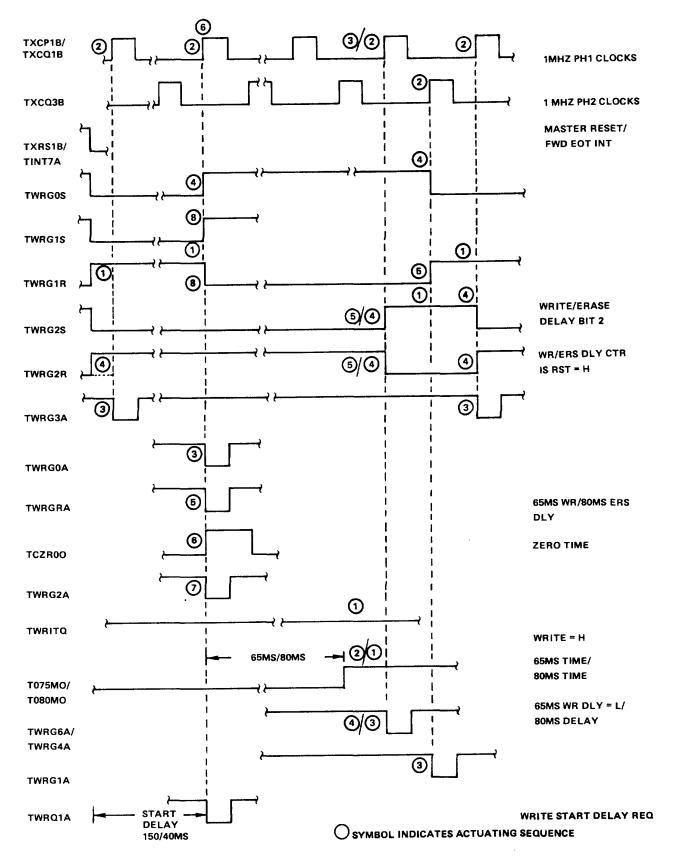

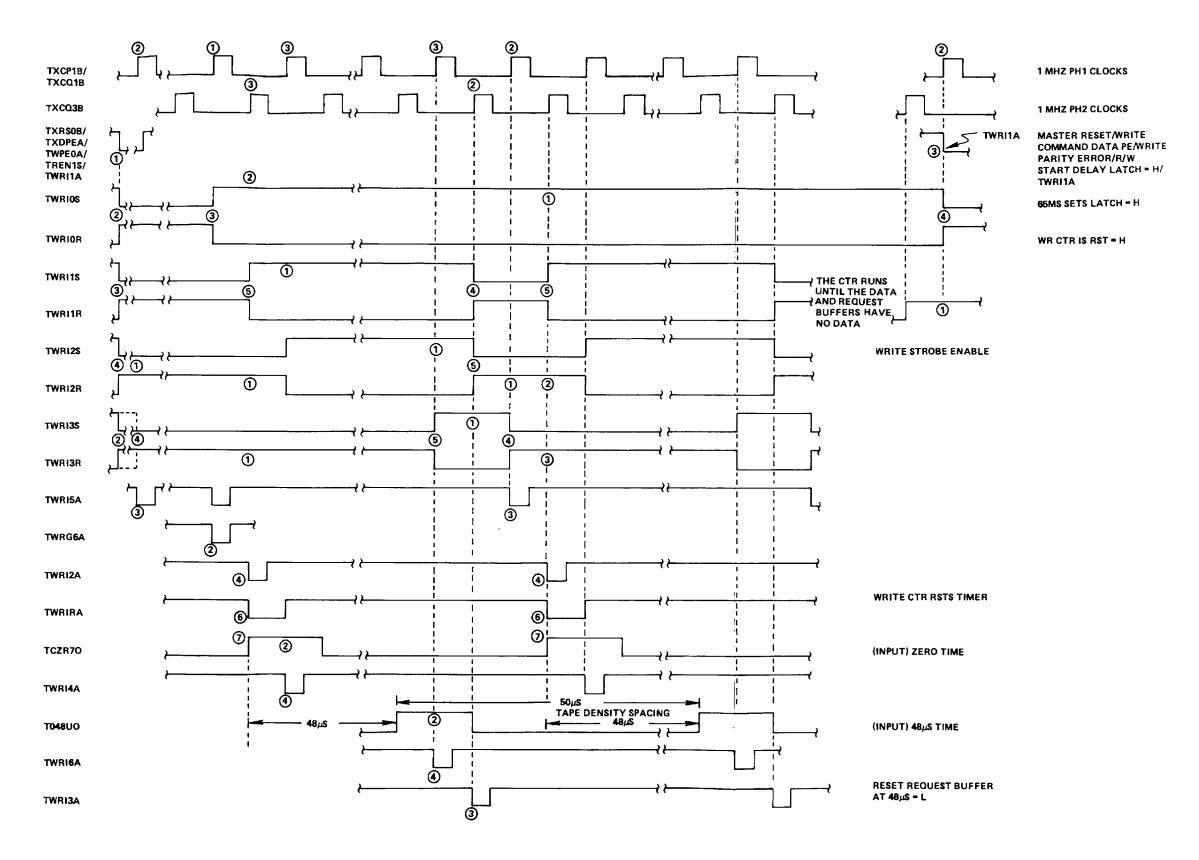

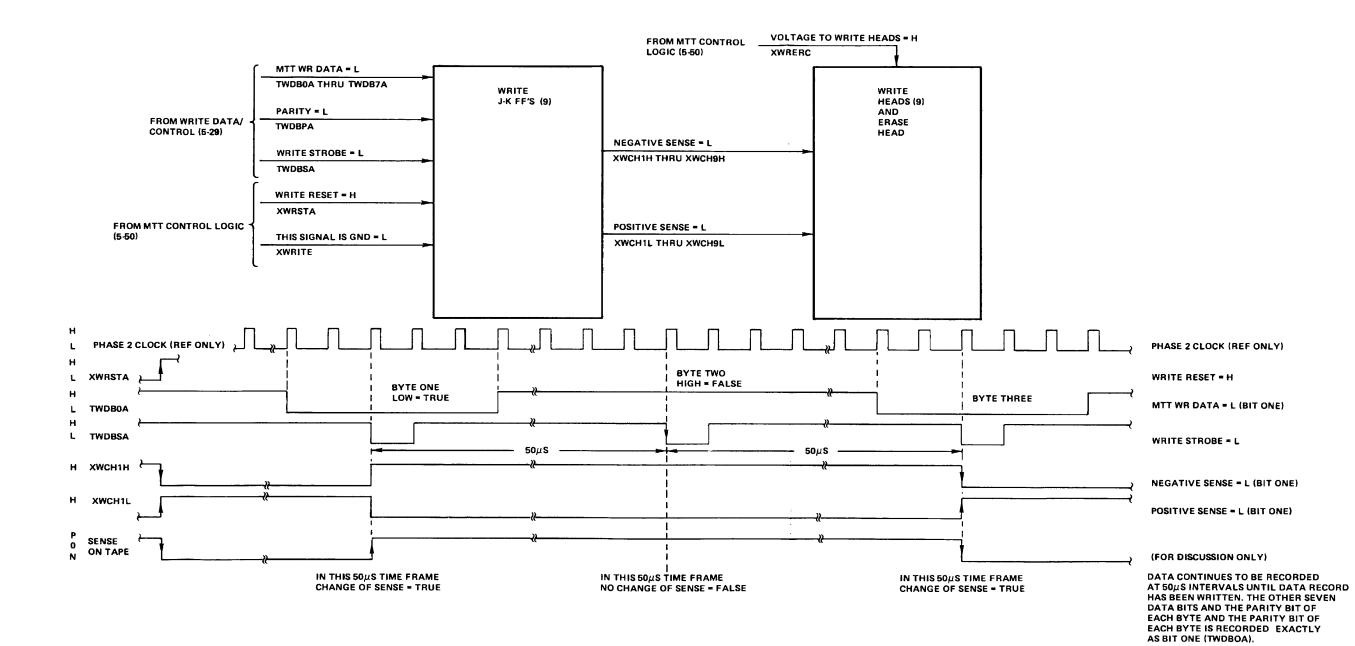

| 5-29. | MTT Write Function Logic                | 5-212 |

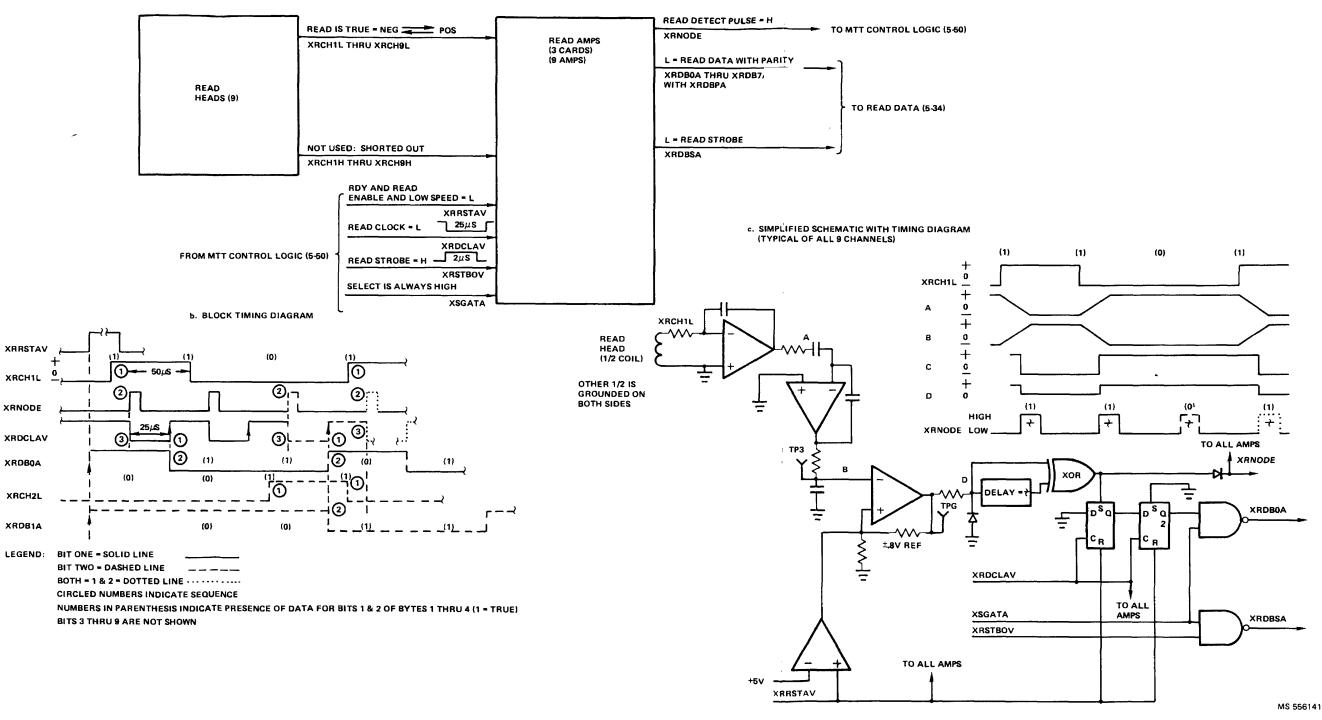

| 5-30. | MTT Read Function Logic                 | 5-215 |

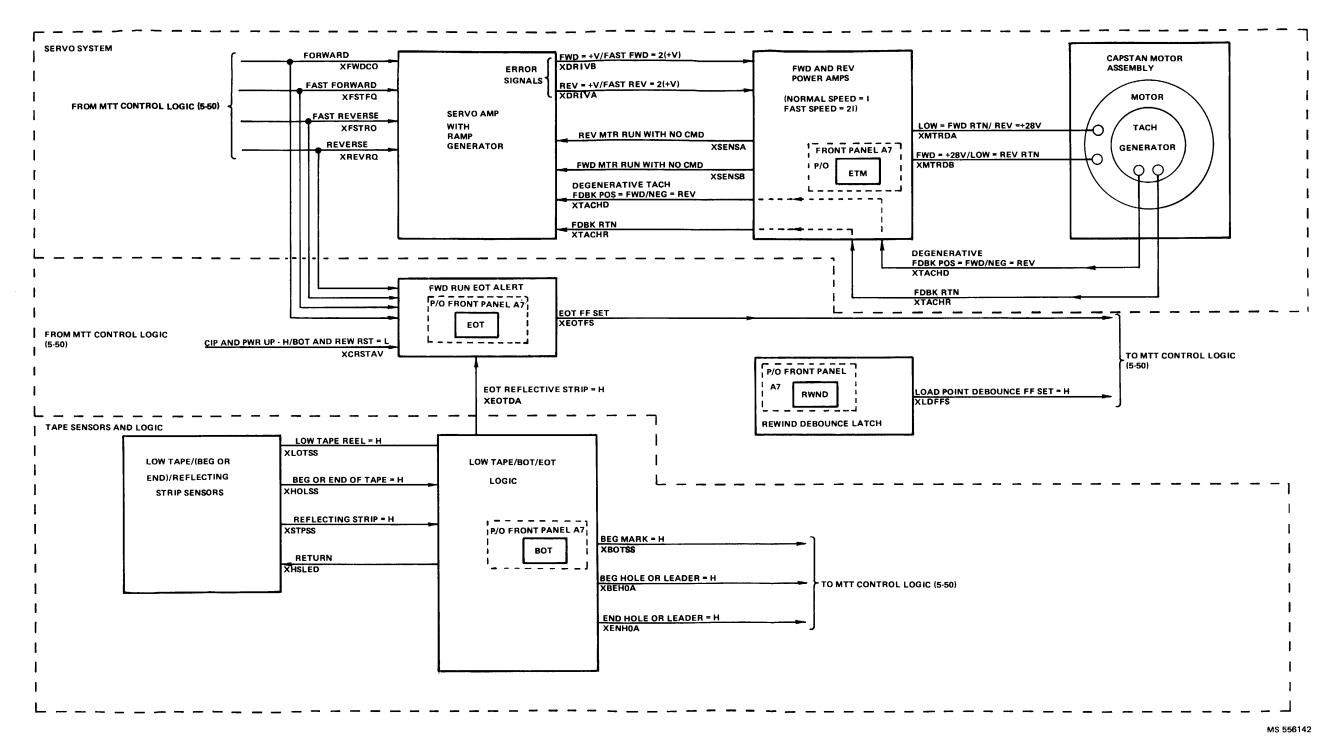

| 5-31. | MTT Tape Drive Electronics              | 5-216 |

|       | •                                       |       |

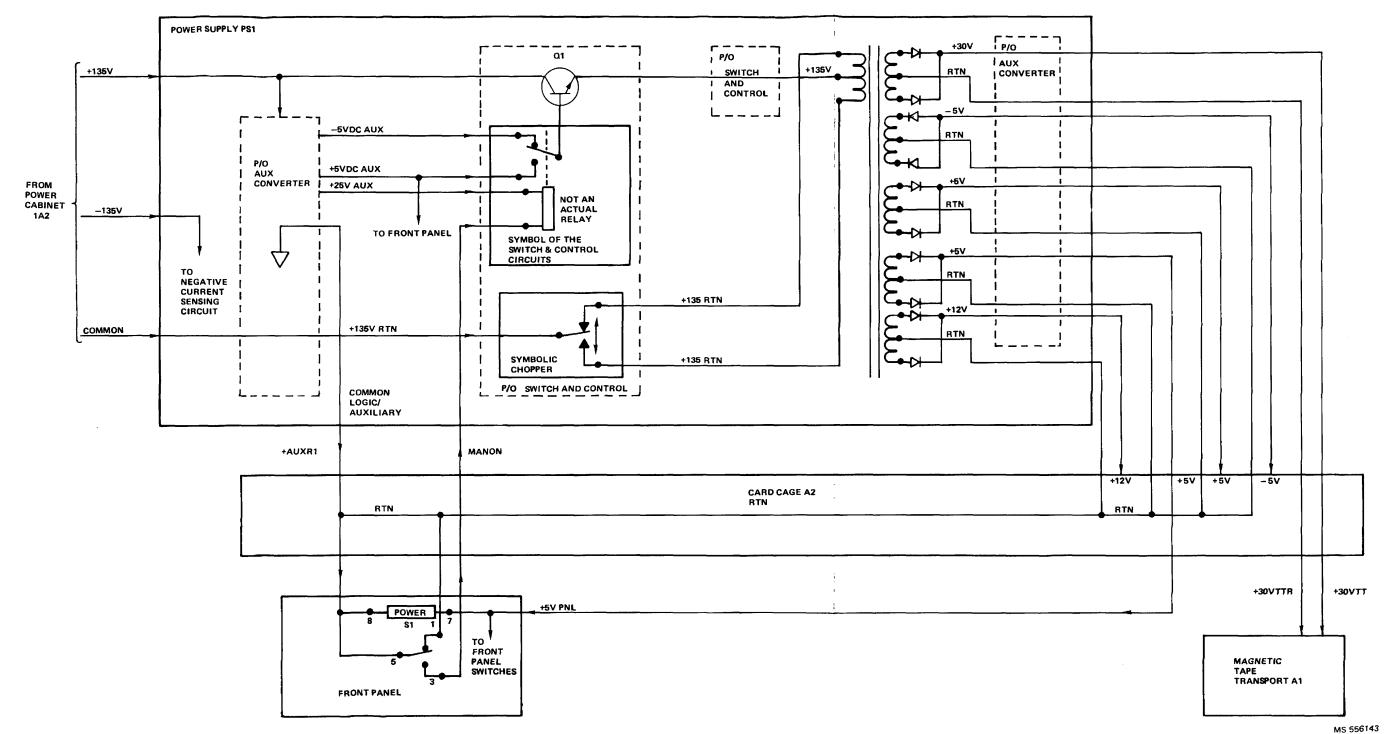

# Section IV. WIRING HARNESSES AND POWER DISTRIBUTION

| 5-32. | W2 Harness and Front Panel Wiring Diagram | 5-222 |

|-------|-------------------------------------------|-------|

|       | MTT Wiring Diagram                        |       |

| 5-34. | W1, W3, and MTS Interface Wiring Diagram  | 5-222 |

| 5-35. | Power Distribution                        | 5-222 |

# ii

# LIST OF ILLUSTRATIONS

| Figure | Title                                                 | Page  |

|--------|-------------------------------------------------------|-------|

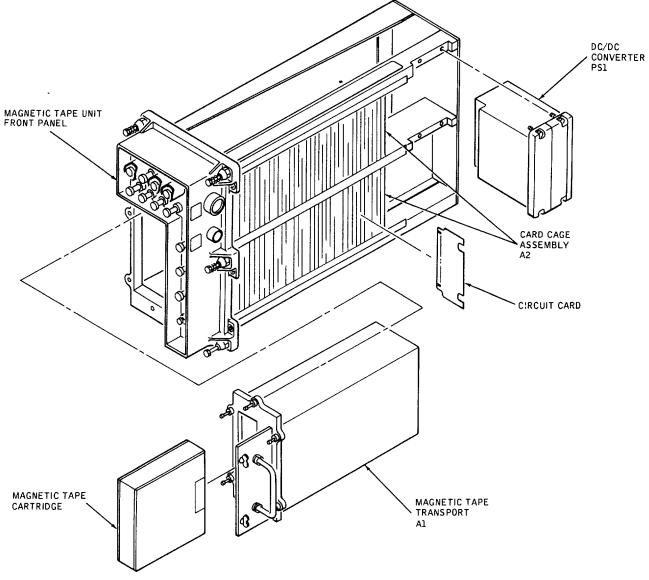

| 5-1.   | MTU Major Subassemblies                               | 5-2   |

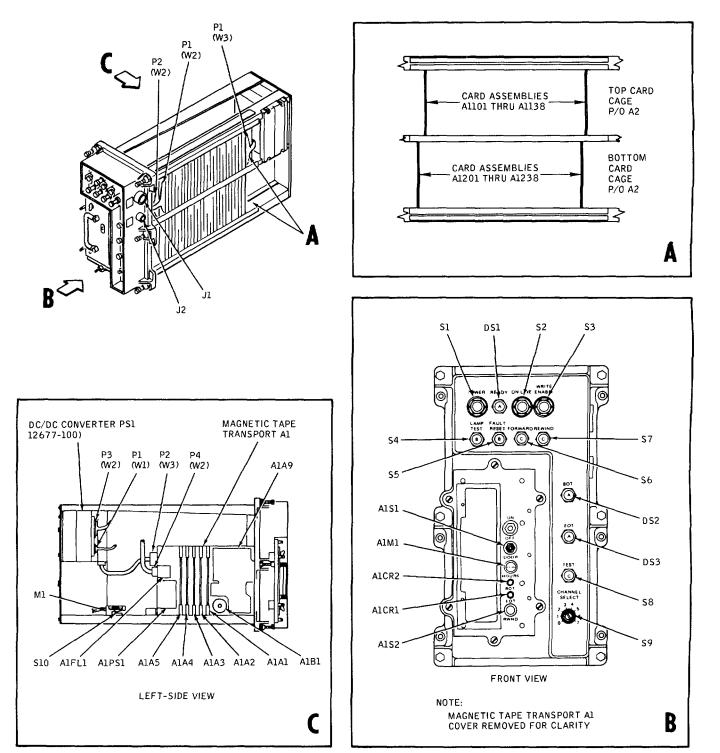

| 5-2.   | MTU Component Location.                               | 5-3   |

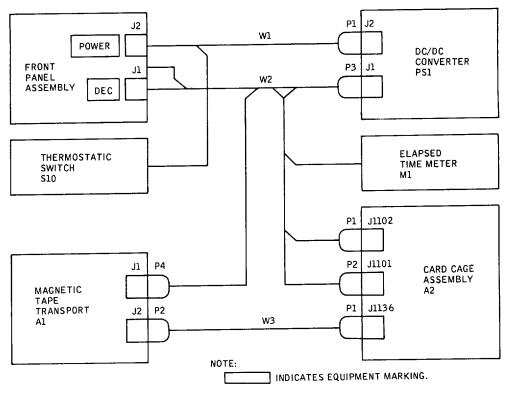

| 5-3.   | MTU Cabling Diagram                                   | 5-5   |

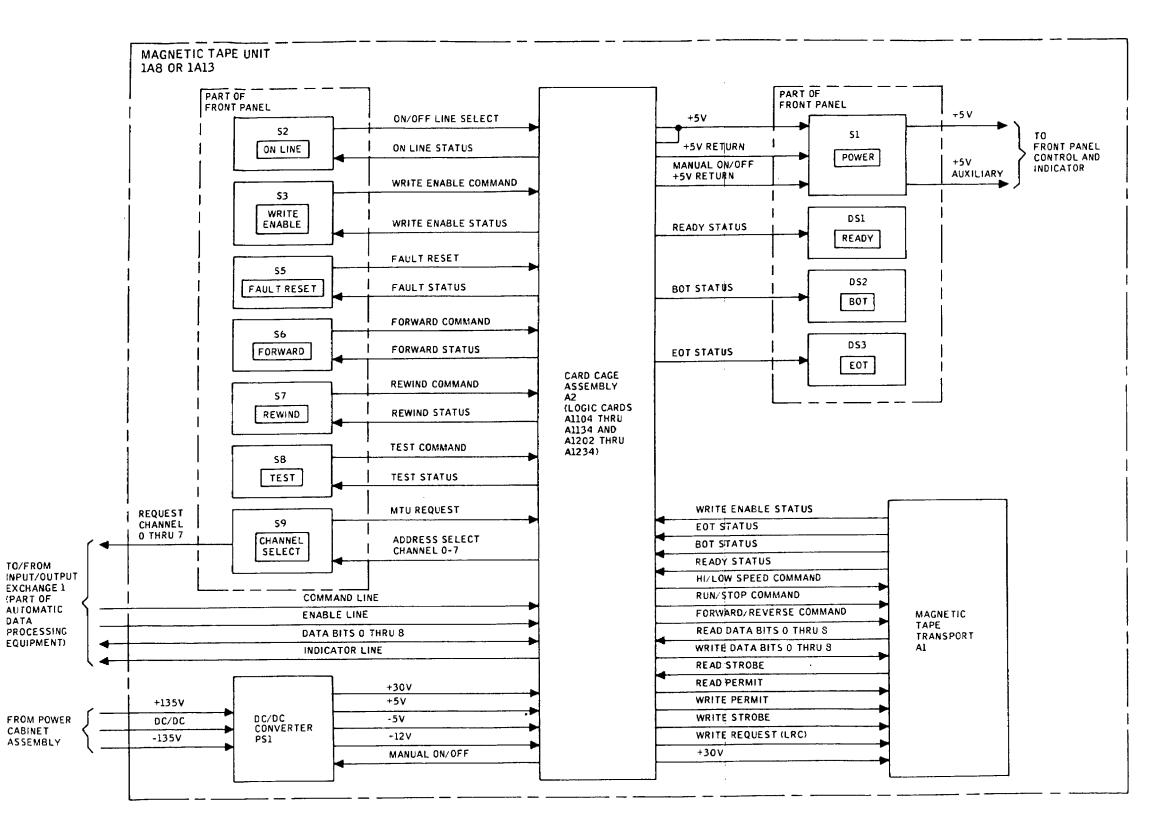

| 5-4.   | MTU Overall Block Diagram                             | 5-85  |

| 5-5.   | MTU Functional Block Diagram                          | 5-87  |

| 5-6.   | Two-Phase Clock Generator Block Diagram               | 5-95  |

| 5-7.   | Main Timing Counter Block Diagram                     |       |

| 5-8.   | Main Timing Counter Timing Diagram                    |       |

| 5-9.   | Input/Output Interface Block Diagram                  |       |

| 5-10.  | Input/Output Data Buffer Block Diagram                |       |

| 5-11.  | Read, Status, or Interrupt Output Logic Block Diagram |       |

| 5-12.  | I/O Strobe and Request Counters Block Diagram         |       |

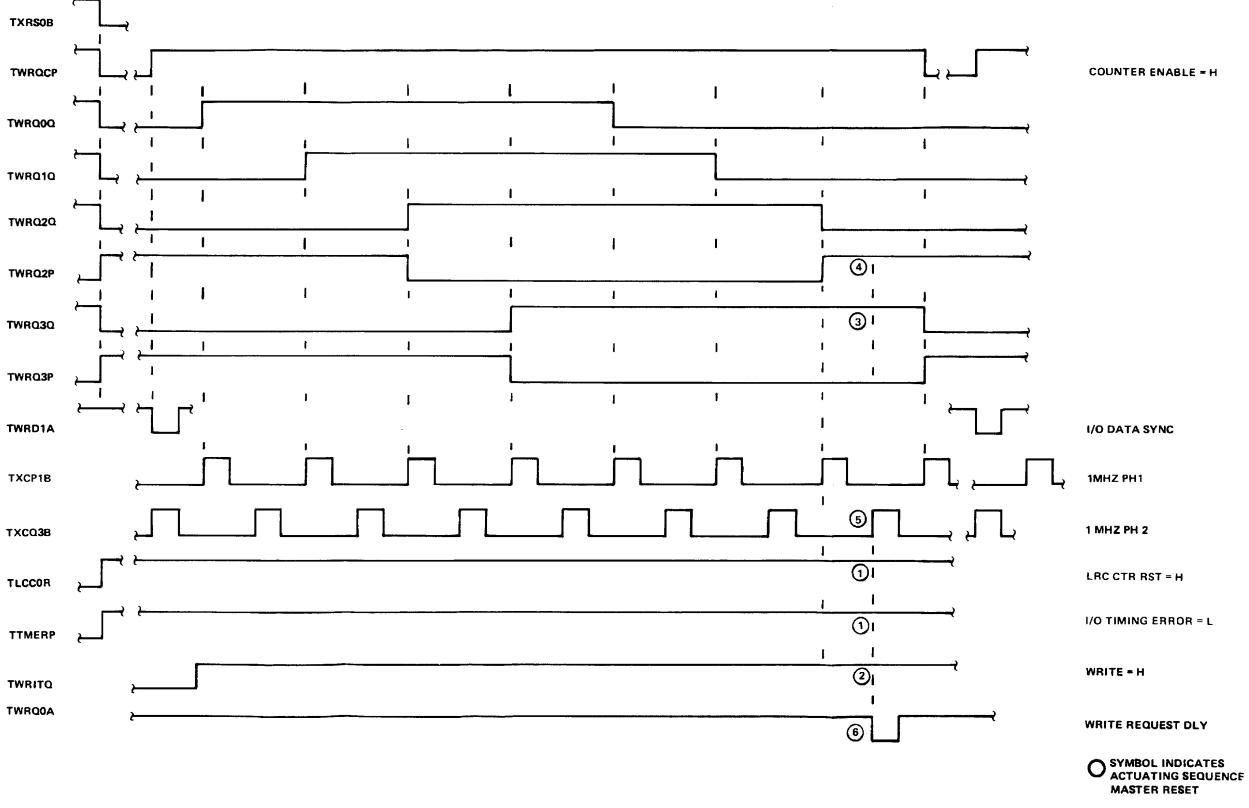

| 5-13.  | Request Counter Timing Diagram                        | 5-113 |

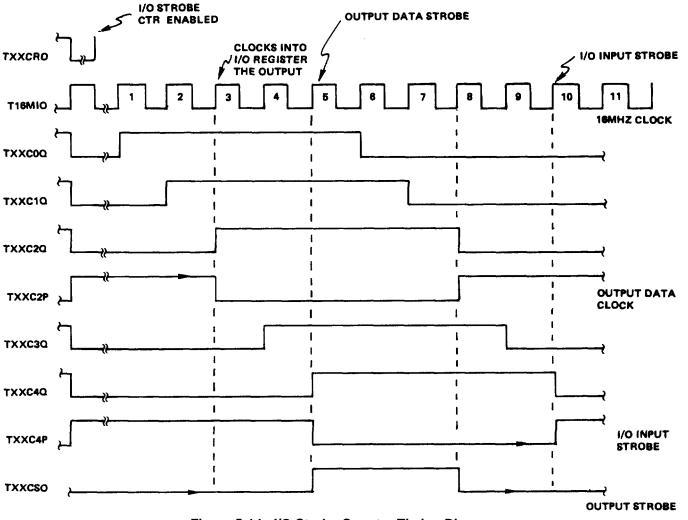

| 5-14.  | I/O Strobe Counter Timing Diagram                     | 5-115 |

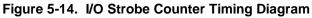

| 5-15.  | State and Byte Counters Block Diagram                 | 5-117 |

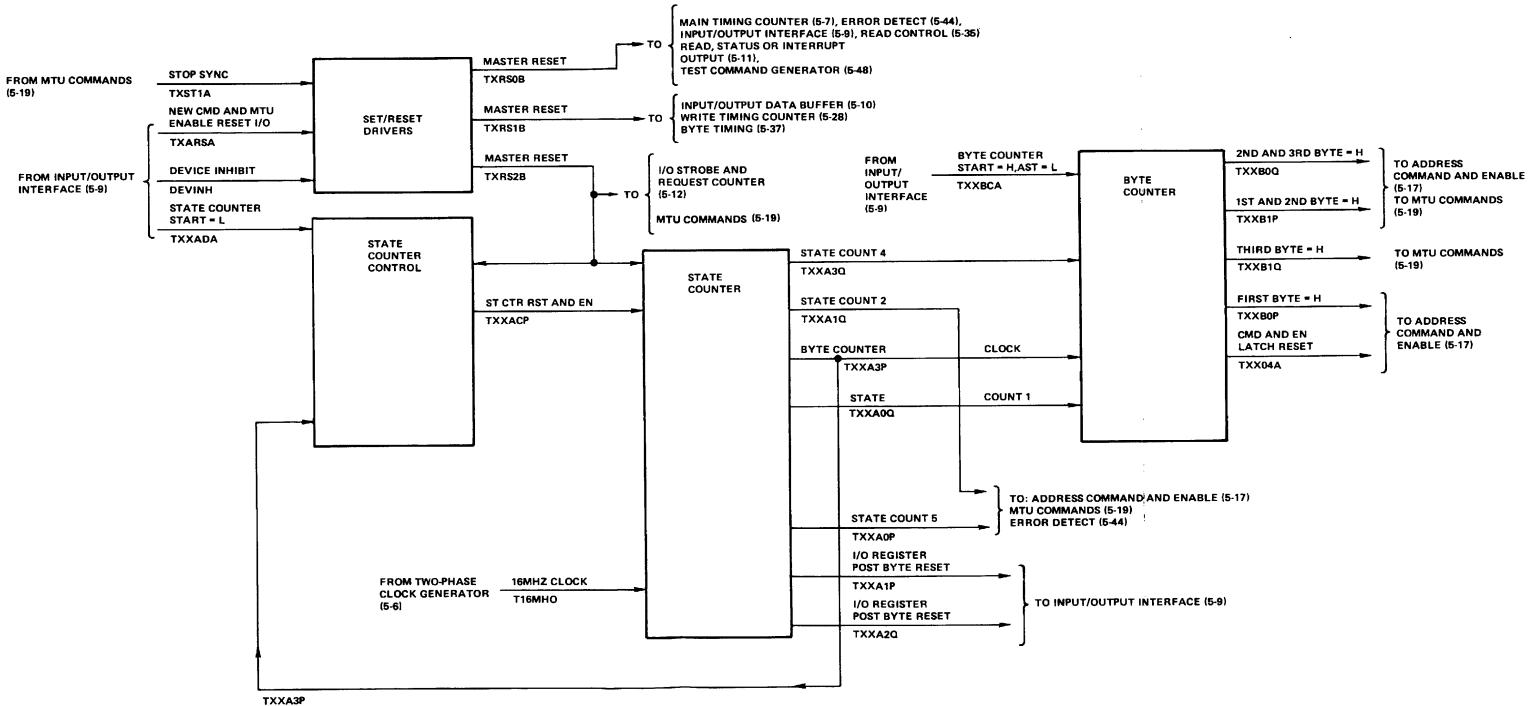

| 5-16.  | State and Byte Counters Timing Diagram                | 5-119 |

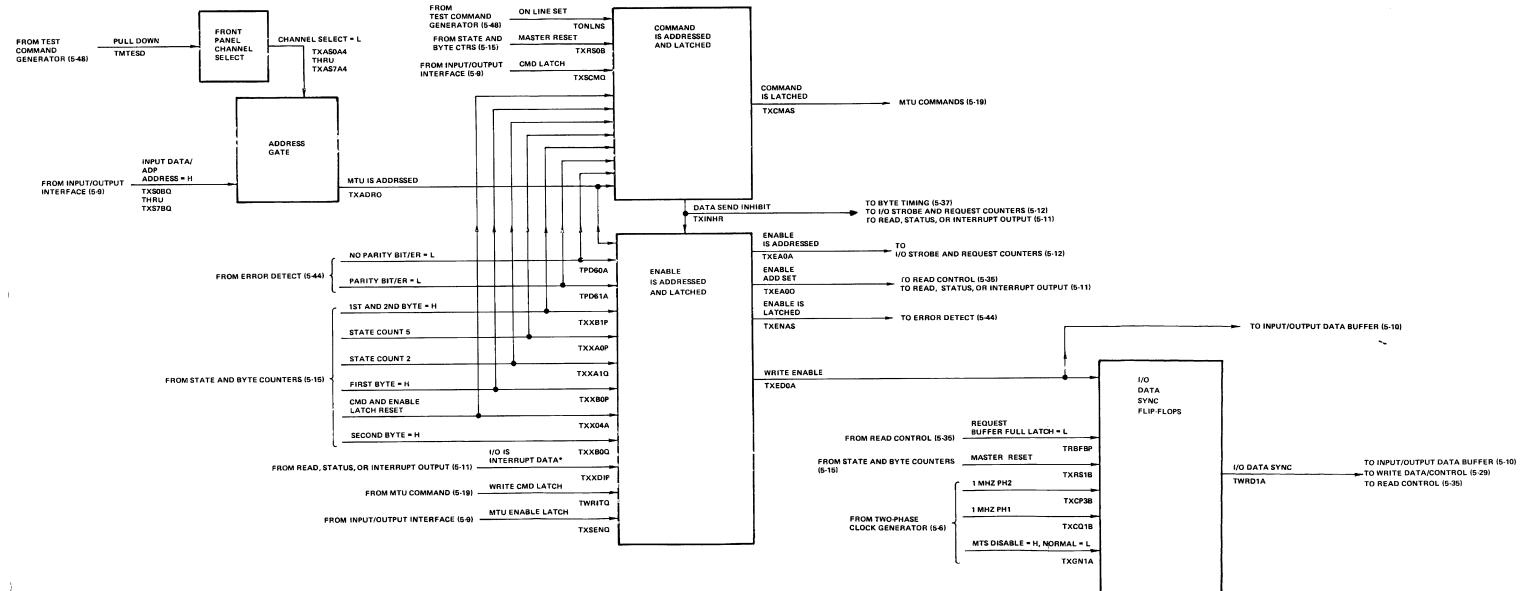

| 5-17.  | Address, Command, and Enable Logic Block Diagram      | 5-121 |

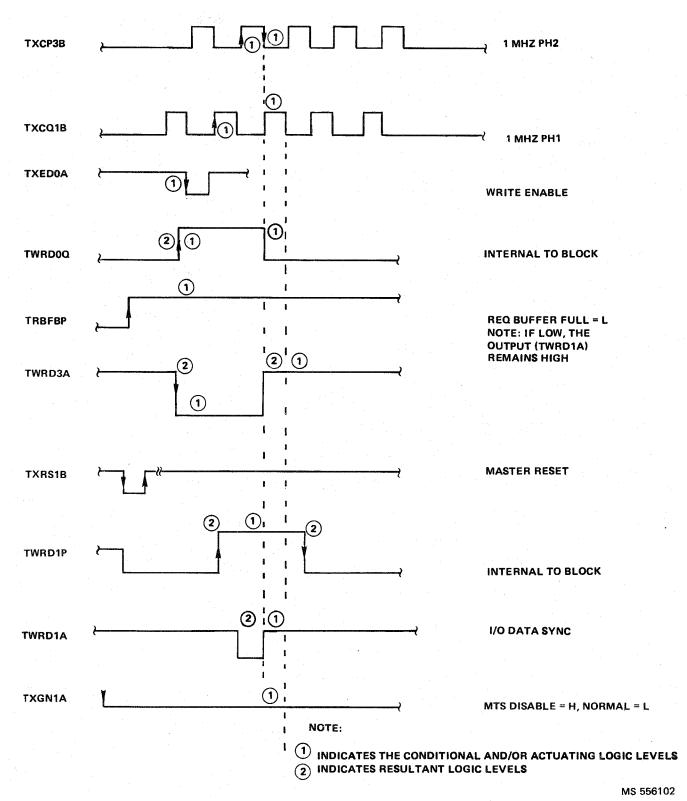

| 5-18.  | I/O Data SYNC Flip-Flops Timing Diagram               |       |

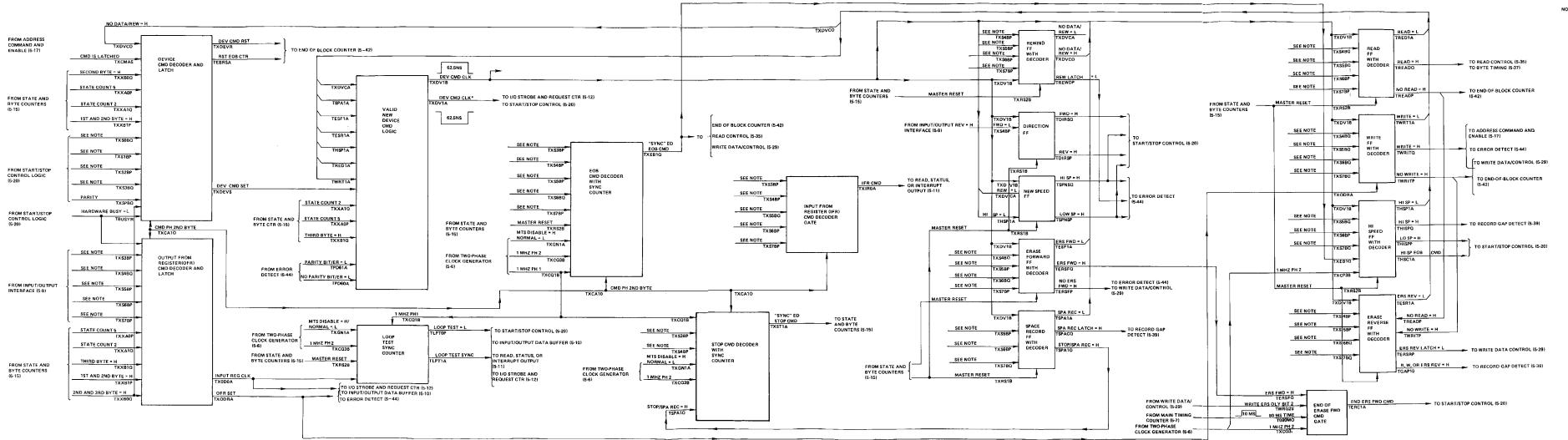

| 5-19.  | MTU Commands Logic Block Diagram                      |       |

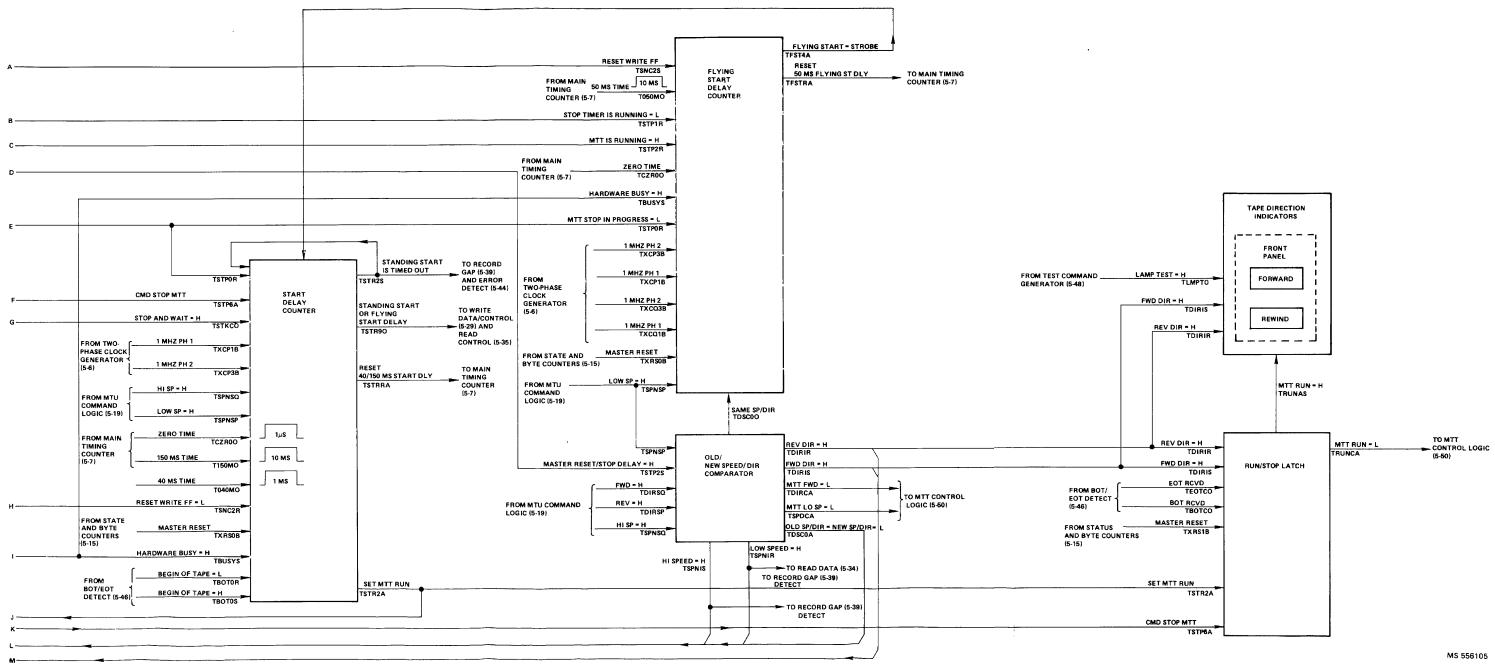

| 5-20.  | Start/Stop Control Logic Block Diagram                |       |

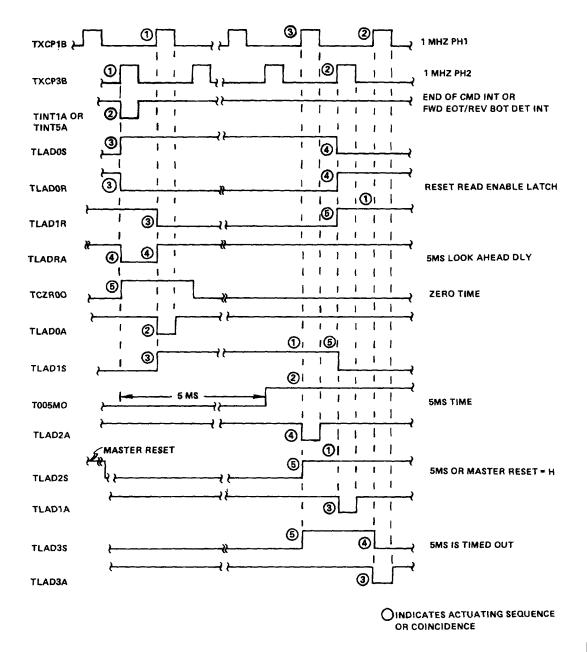

| 5-21.  | Look Ahead Delay Counter Timing Diagram               |       |

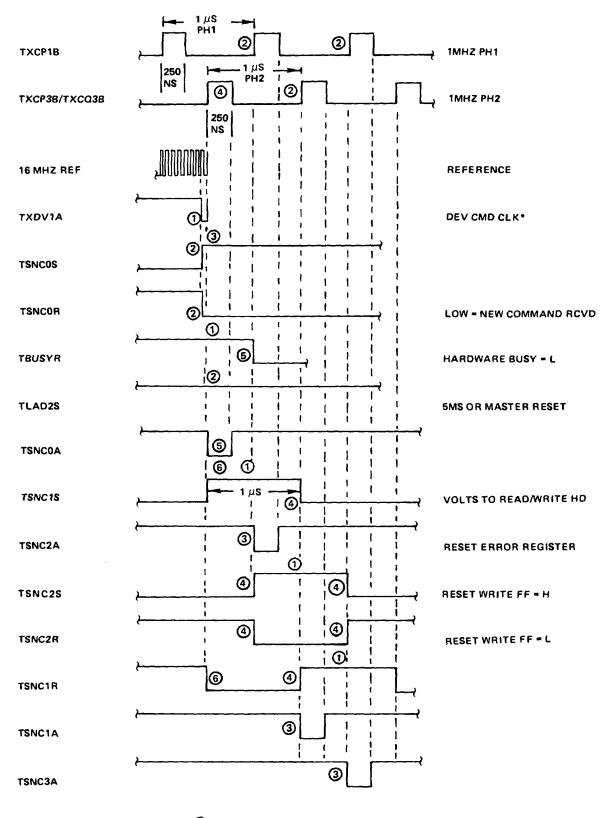

| 5-22.  | DEV CMD SYNC Counter Timing Diagram                   |       |

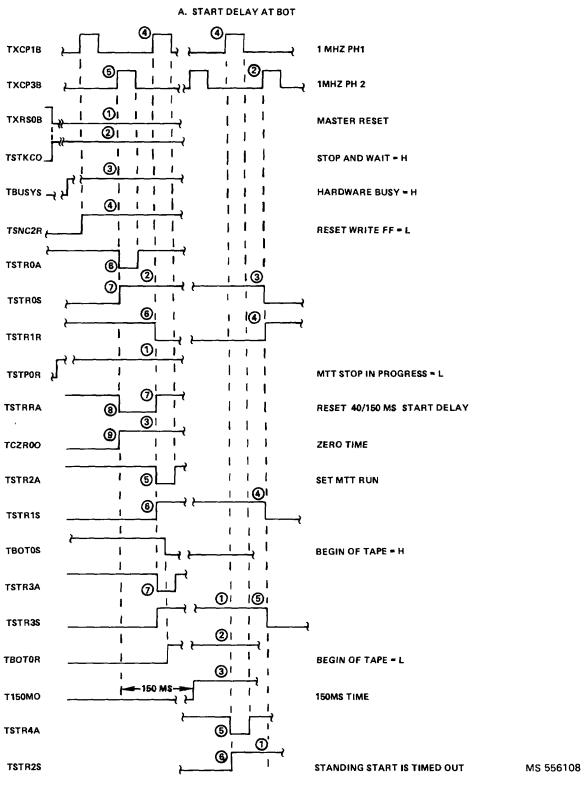

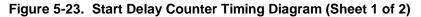

| 5-23.  | Start Delay Counter Timing Diagram                    |       |

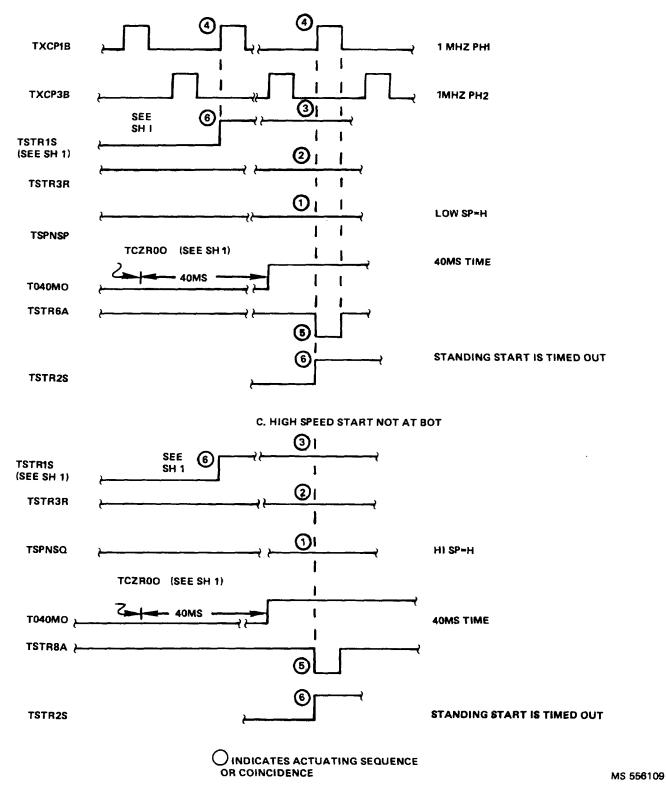

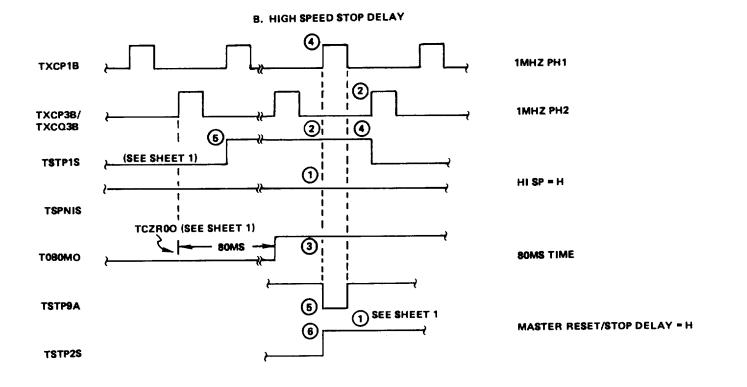

| 5-24.  | Stop Delay Counter Reset Timing Diagram               | 5-141 |

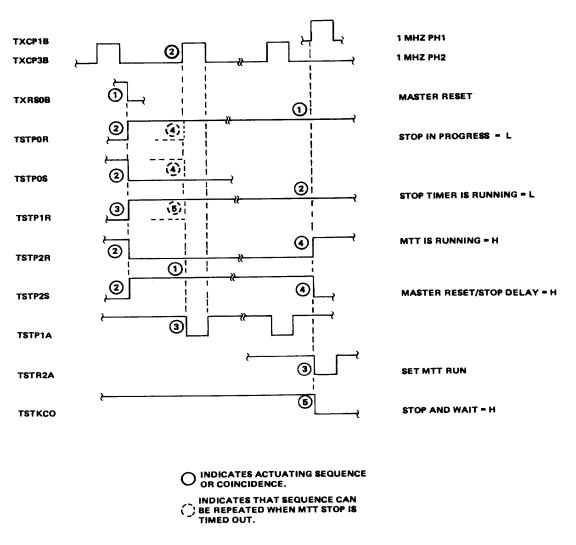

| 5-25.  | Stop Delay Counter Timing Diagram                     | 5-142 |

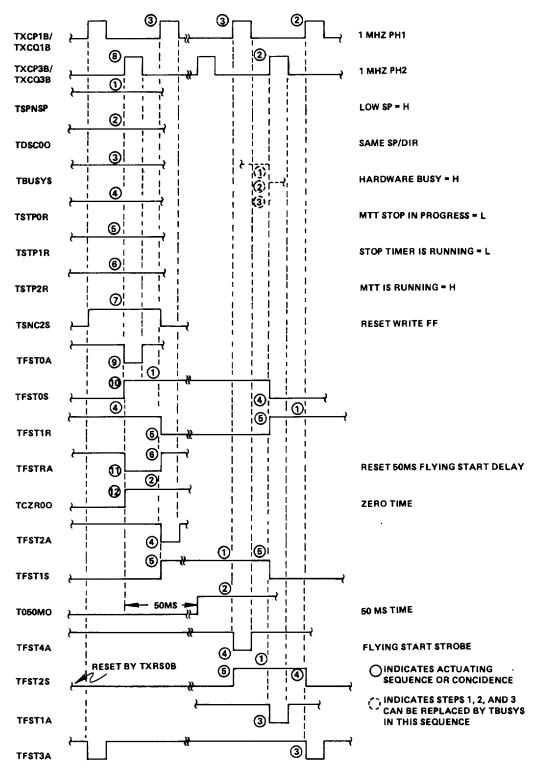

| 5-26.  | Flying Start Delay Counter Timing Diagram             | 5-145 |

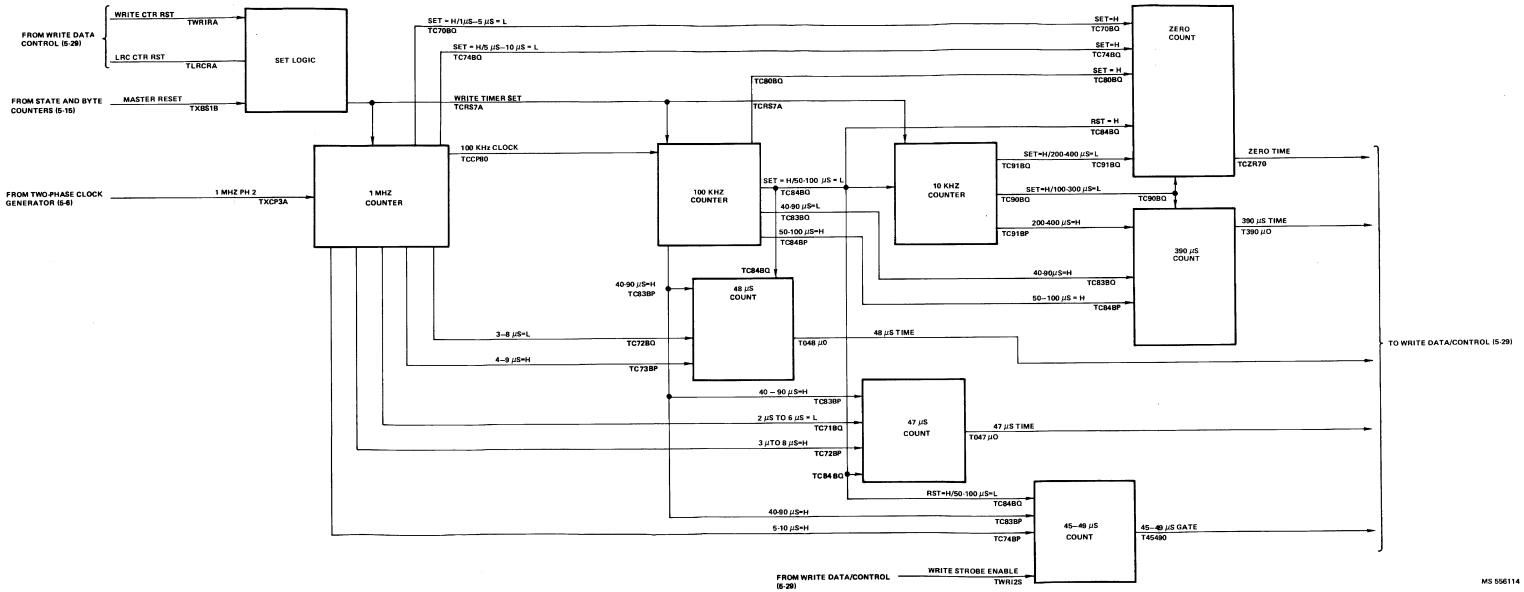

| 5-27.  | Write Timing Counter Block Diagram                    | 5-147 |

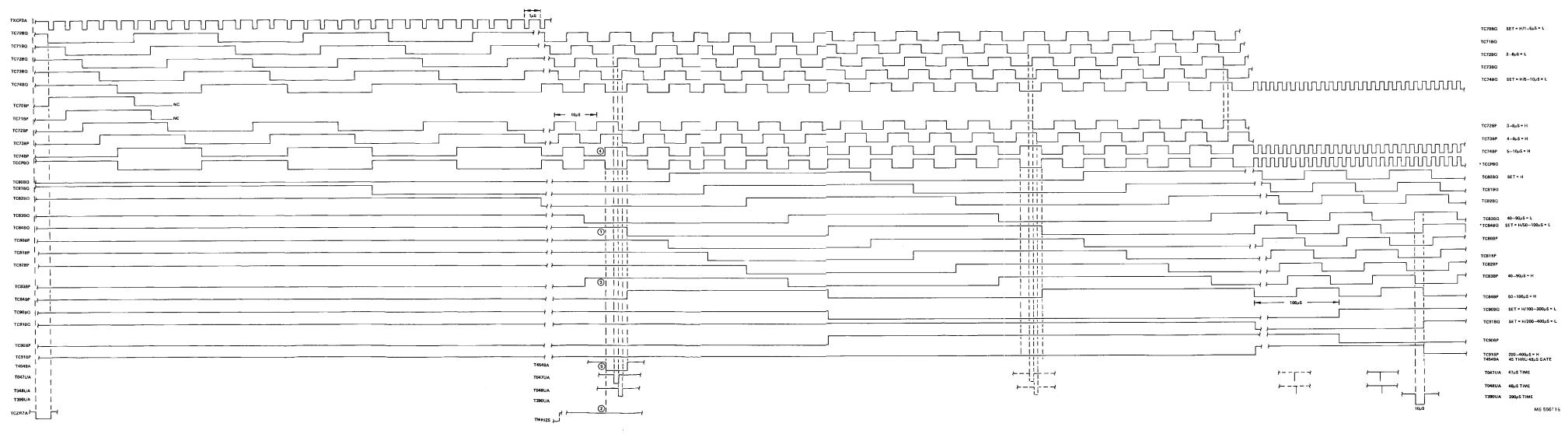

| 5-28.  | Write Timing Counter Timing Diagram                   | 5-149 |

| 5-29.  | Write Data/Control Block Diagram                      | 5-153 |

| 5-30.  | Write/Erase Delay (65/80-ps) Timing Diagram           | 5-157 |

| 5-31.  | Write Counter Timing Diagram                          |       |

| 5-32.  | Write Request Delay Counter Timing Diagram            |       |

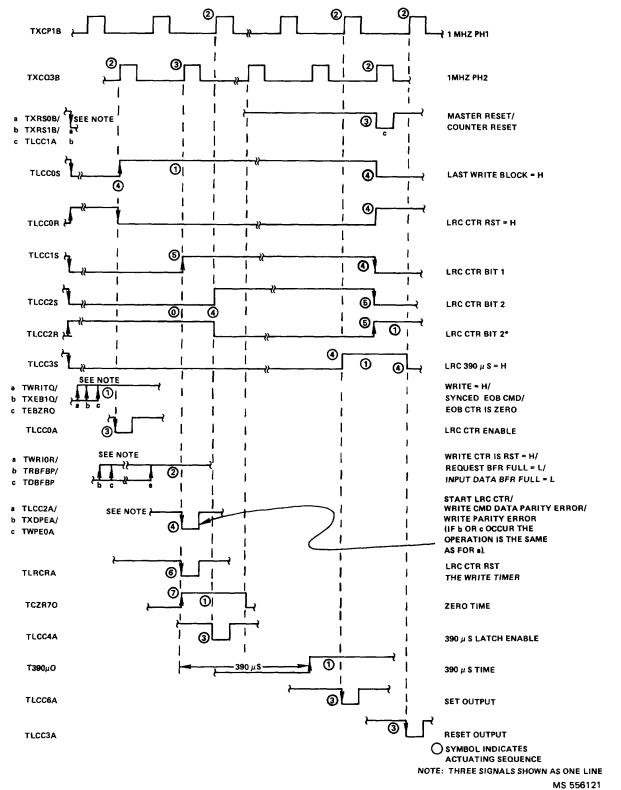

| 5-33.  | LRC Counter Timing Diagram                            |       |

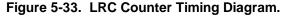

| 5-34.  | Read Data Logic Block Diagram                         |       |

| 5-35.  | Read Control Logic Block Diagram                      |       |

| 5-36.  | Read Request Timing Diagram                           |       |

| 5-37.  | Read Byte Timing Logic Block Diagram                  | 5-173 |

| 5-38.  | Read Byte Counter Timing Diagram                      | 5-175 |

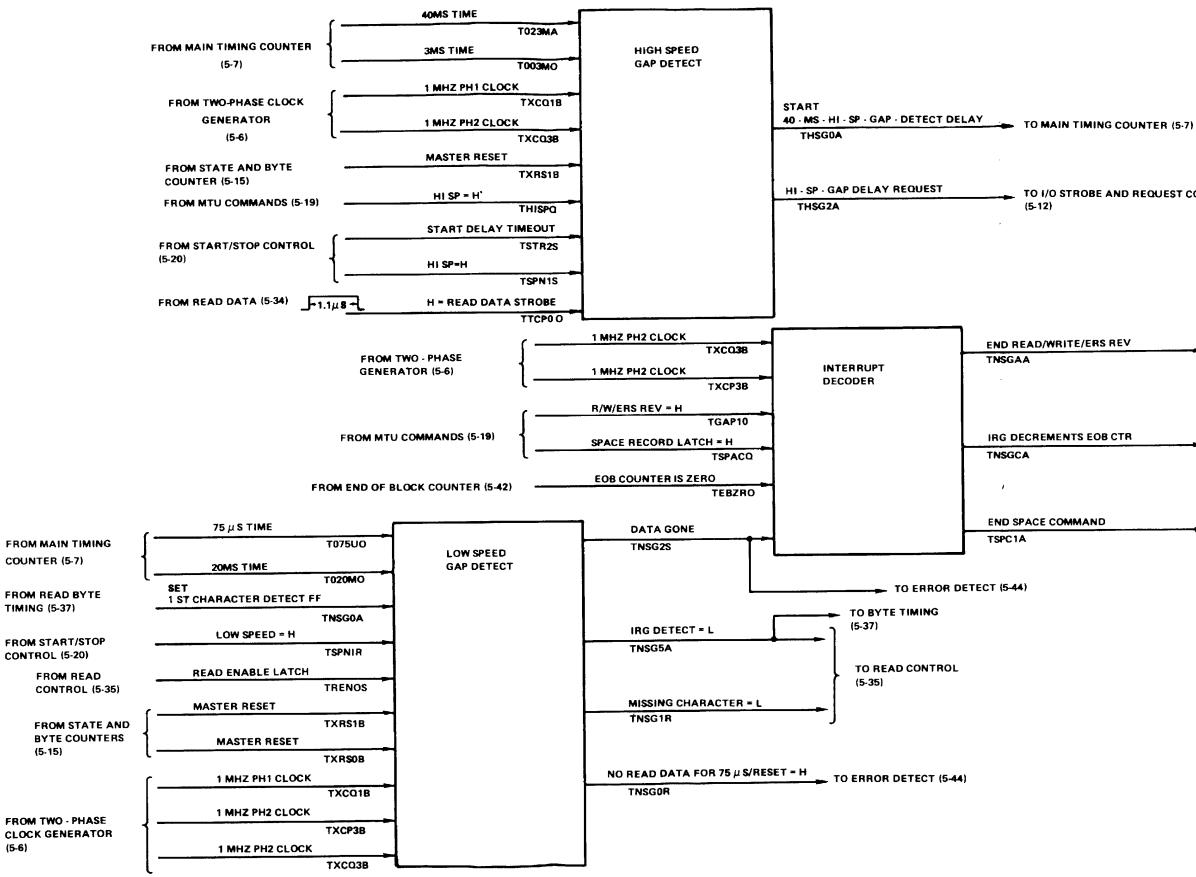

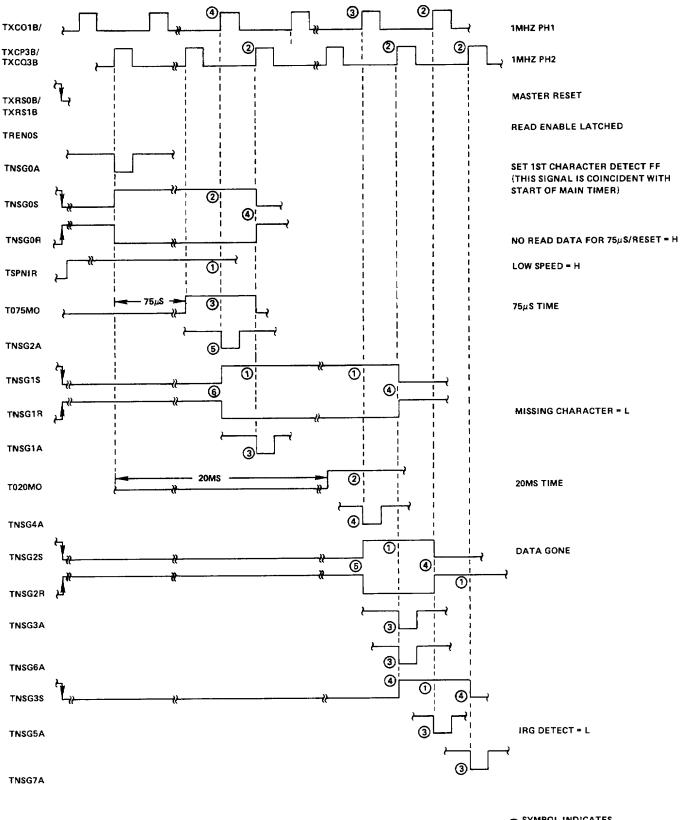

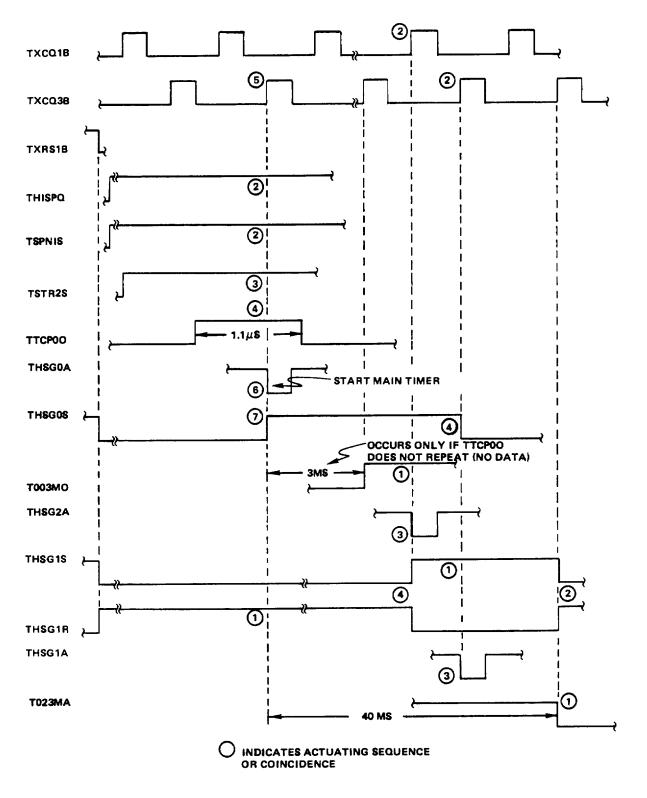

| 5-39.  | Record Gap Detect Logic Block Diagram                 | 5-177 |

| 5-40.  | Record Gap Detect Timing Diagram                      | 5-179 |

| 5-41.  | High Speed Gap Detect Timing Diagram                  | 5-181 |

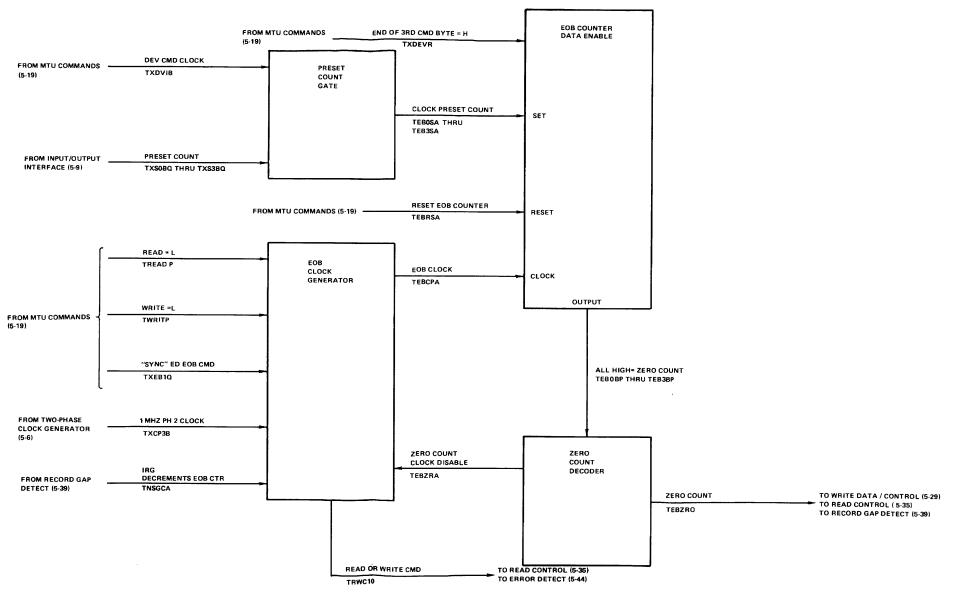

| 5-42.  | EOB Counter Block Diagram                             | 5-183 |

| 5-43.  | EOB Counter Timing Diagram                            | 5-185 |

| 5-44.  | Error Detect Logic Block Diagram                      | 5-187 |

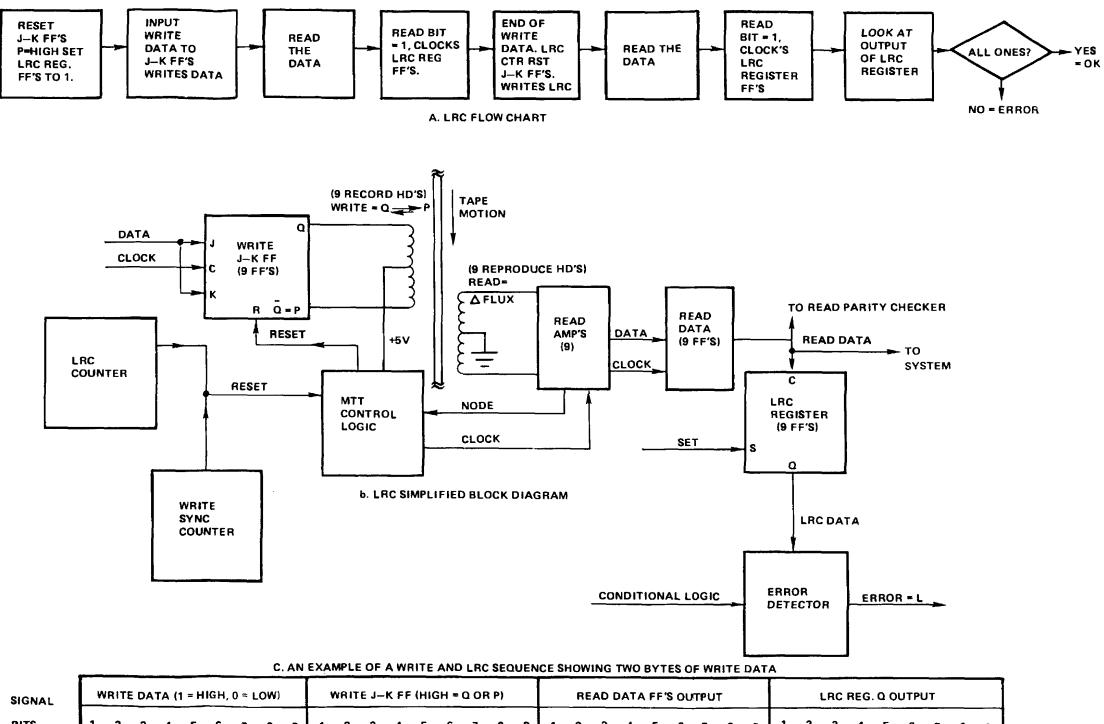

| 5-45.  | Longitudinal Redundancy Check Logic Block Diagram     | 5-191 |

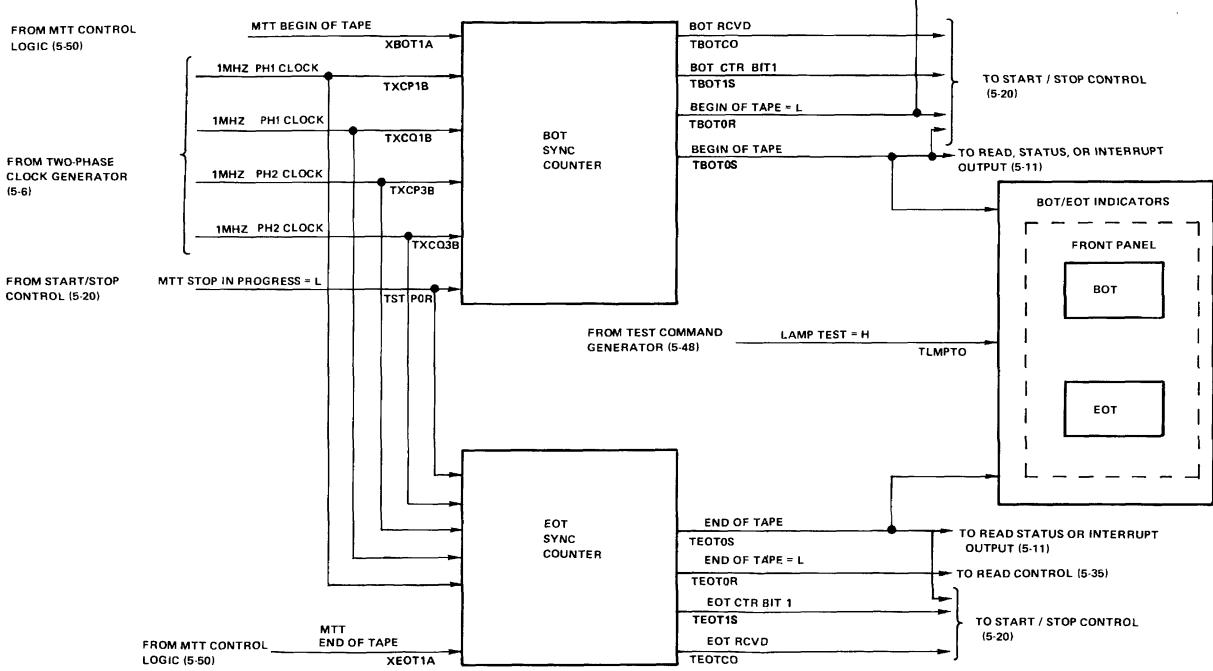

| 5-46.  | BOT/EOT Detect Logic Block Diagram                    | 5-199 |

| 5-47.  | BOT/EOT SYNC Counters Timing Diagram                  | 5-201 |

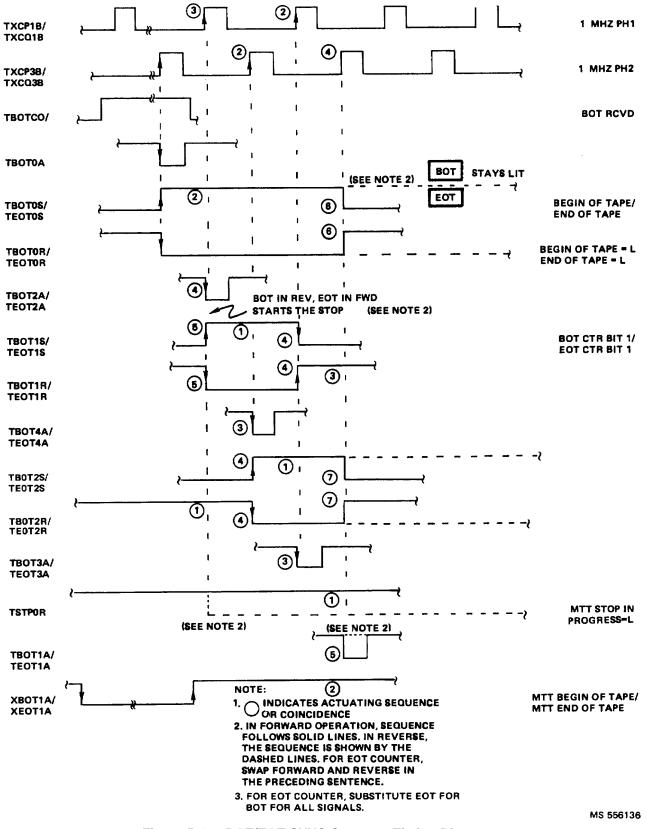

| 5-48.  | Test Command Generator Block Diagram                  | 5-203 |

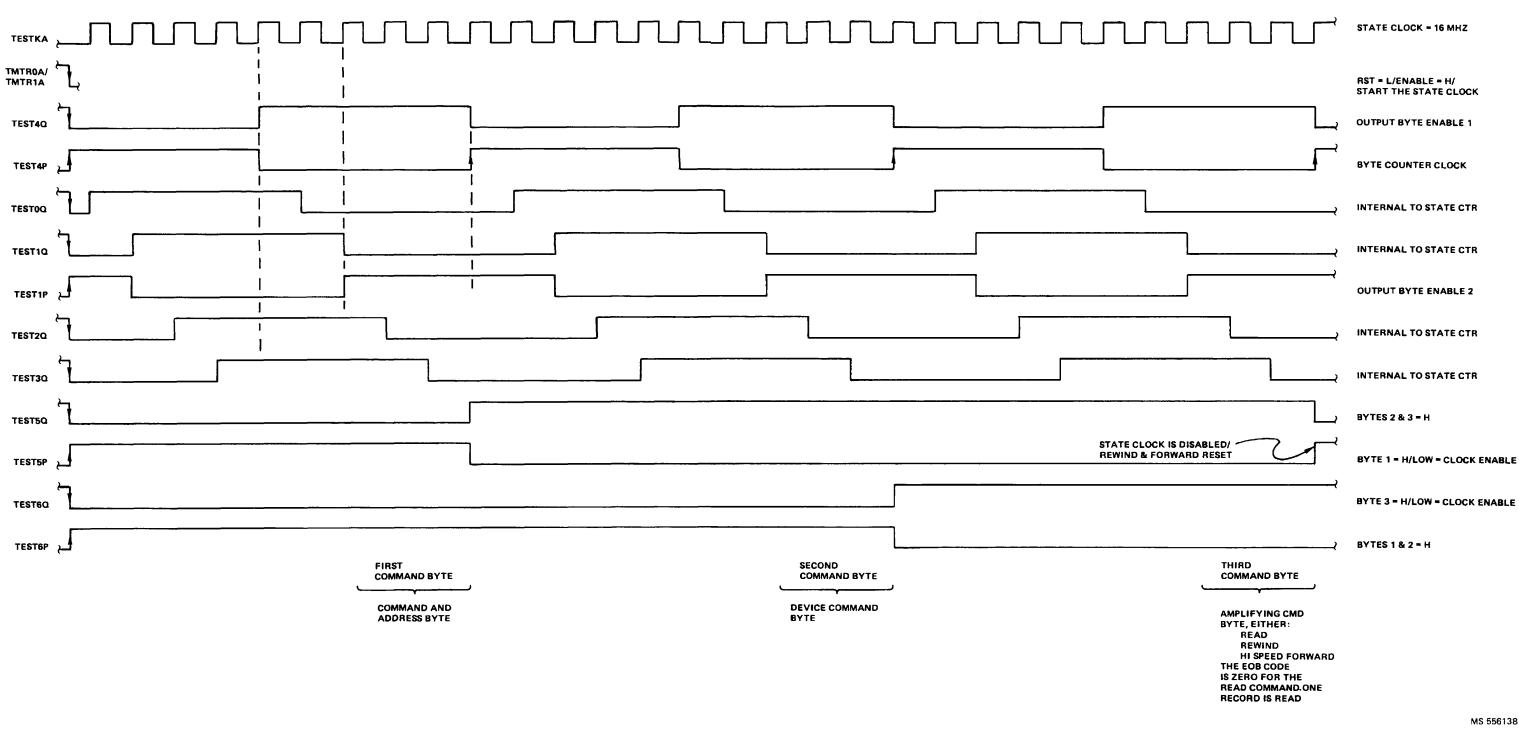

| 5-49.  | Test Commands Timing Diagram                          | 5-205 |

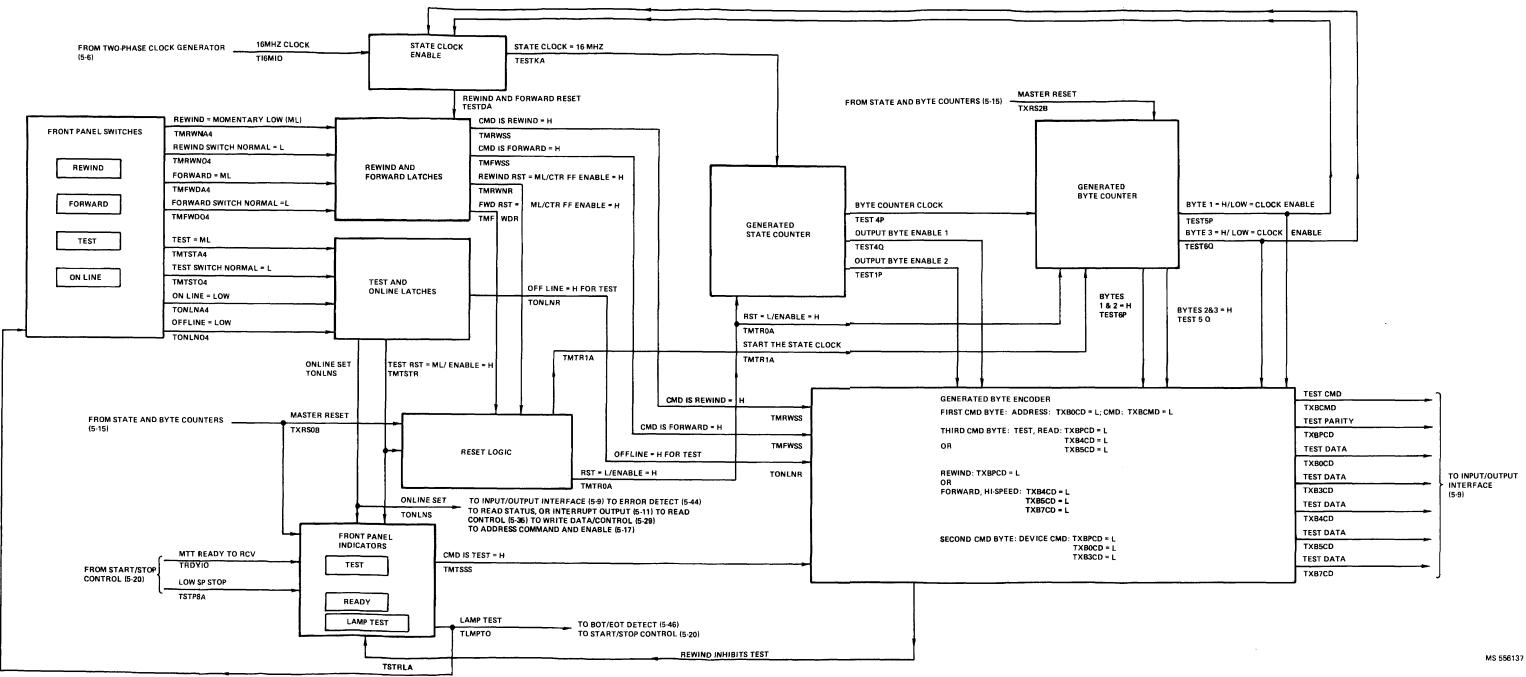

| 5-50.  | MTT Control Logic Block Diagram                       | 5-209 |

| 5-51.  | MTT Write Function Block Diagram                      | 5-213 |

| 5-52.  | MTT Read Function Block Diagram                       | 5-217 |

| 5-53.  | MTT Tape Drive Electronics Block Diagram              | 5-219 |

| 5-54.  | Power Distribution Block Diagram                      | 5-223 |

|        | -                                                     |       |

Page

# **LIST OF ILLUSTRATIONS - Continued**

| Figure | Title                                                      |

|--------|------------------------------------------------------------|

| FO-1.  | Two-Phase Clock Generator Logic Diagram                    |

| FO-2.  | Main Timing Counter Logic Diagram                          |

| FO-3.  | Input/Output Interface Logic Diagram                       |

| FO-4.  | Input/Output Data Buffer Logic Diagram                     |

| FO-5.  | Read, Status, or Interrupt Output Logic Diagram            |

| FO-6.  | I/O Strobe and Request Counter Logic Diagram               |

| FO-7.  | State and Byte Counters Logic Diagram                      |

| FO-8.  | Address, Command, and Enable Logic Diagram                 |

| FO-9.  | MTU Commands Logic Diagram                                 |

| FO-10. | Start/Stop Control Logic Diagram                           |

| FO-11. | Write Timing Counter Logic Diagram                         |

| FO-12. | Write Data/Control Logic Diagram                           |

| FO-13. | Read Data Logic Diagram                                    |

| FO-14. | Read Control Logic Diagram                                 |

| FO-15. | Read Byte Timing Logic Diagram                             |

| FO-16. | Record Gap Detect Logic Diagram                            |

| FO-17. | End of Block Counter Logic Diagram                         |

| FO-18. | Error Detect Logic Diagram                                 |

| FO-19. | BOT/ELT Detect Logic Diagram                               |

| FO-20. | Test Command Generator Logic Diagram                       |

| FO-21. | MTT Control Logic Diagram                                  |

| FO-22. | MTT Write Function Logic Diagram                           |

| FO-23. | MTT Read Function Logic Diagram                            |

| FO-24. | MTT Tape Drive Electronics Signal Flow Diagram             |

| FO-25. | W2 Harness and Front Panel Wiring Diagram                  |

| FO-26. | MTT Wiring Diagram                                         |

| FO-27. | WI, W3, and Module Test Set (MTS) Interface Wiring Diagram |

| FO-28. | MTU Power Distribution Diagram                             |

| FO-29. | MTT Power Distribution Diagram                             |

|        |                                                            |

iv

# LIST OF TABLES

| Table | Title                                 | Page  |

|-------|---------------------------------------|-------|

| 5-1.  | Card Location in Logic Diagrams Index | 5-6   |

| 5-2.  | Key Signal Lookup Listing             |       |

| 5-3.  | Timing Decoder Truth Table            | 5-176 |

| 5-4.  | IRG Interrupt Decoder Truth Table     | 5-180 |

| 5-5.  | I/O Parity Truth Table                | 5-195 |

| 5-6.  | Set Error Register Inputs and Outputs | 5-197 |

| 5-7.  | Generated Byte Encoder Truth Table    | 5-208 |

# v / (vi blank)

#### CHAPTER 5

# MAGNETIC TAPE UNIT EXPANDED TROUBLESHOOTING

# Section I. INTRODUCTION

**5-1. Scope.** The expanded troubleshooting part of TM 9-1430-655-20-5 of the Recorder-Reproducer RD-449/TSQ-73(V), hereinafter referred to as the magnetic tape unit (MTU), Equipment Maintenance for Guided Missile Air Defense System AN/ TSQ-73 is contained in volumes 2 and 3. It provides supplemental information for the use and guidance of advanced personnel responsible for repair of the MTU beyond the scope of organizational maintenance covered in the basic TM 9-1430-655-20 series of technical manuals.

**5-2. Expanded Troubleshooting Concept.** Expanded troubleshooting is required when existing fault isolation procedures in the basic manuals fail to isolate and correct a malfunction. The troubleshooting covered in this manual is based on the use of existing onsite equipment (tapes, tools, test equipment, spare parts, and publications). Isolation of malfunctions is based on the fault analysis of normal system operating conditions and the use of built-in maintenance and diagnostic (M&D) software programs.

**5-3. Troubleshooting Aids.** Volume 2 contains the detailed descriptions and the related functional block diagrams. The functional block diagrams are related to the functional logic diagrams in volume 3 by the titles of the functional areas. Power distribution diagrams, cabling diagrams, and front-panel schematic diagrams are also supplied in volume 3.

a. Input/Output Tables. Input and output tables are provided, as applicable, for each figure and sheet to enable easy access to signals referenced to other diagrams.

*b. Input/Output Symbols.* Symbols used on diagrams to indicate input and output signals include the following: \*

- ▲ Indicates input from another figure.

- $\Delta$  Indicates input from the same figure.

- Indicates output to another figure.

- □ Indicates output to the same figure.

- Indicates output to the same and another figure.

- ← Indicates bidirectional signal flow.

*c.* Equipment Interface. The troubleshooting diagrams may reference inputs and outputs interfacing between other pieces of equipment. When a notation shows that external equipment is involved, it is assumed that the user will refer to the applicable troubleshooting information provided for that equipment.

*d. Logic Symbols.* Logic symbols depend on card types. For discrete circuit cards containing conventional integrated circuits, conventional logic symbols are used. These symbols are used independently, with card locations and card pin numbers notated with the symbol. For analog circuits, circuit card details are provided only to functional level.

**5-4.** Physical Description (fig. 5-1). The MTU includes magnetic tape transport AI and an associated tape cartridge, card cage assembly A2, dc/dc converter PS 1, and a front-panel assembly containing switches, indicators, and external interface connectors. Locations and reference designations of major components of the MTU are shown in figure 5-2. The MTU major subassemblies are described in the following subparagraphs.

a. Front Panel Assembly (fig. 5-2). The front panel assembly contains all controls and indicators required for operation of the MTU. The controls and indicators permit the operator to place the MTU under automatic data processor (ADP) control, enable the write logic, advance or rewind the tape, enable the faultdetect logic, and perform self-test operations. External interface to the MTU is provided through device exchange channel (DEC) connector J 1 and POWER connector J2 mounted on the right side of the front-Connector J1 provides signal panel assembly. connections between the MTU and ADP and also provides an interlock that makes sure that the interconnecting cable is terminated. Connector J2 provides dc power connections between the MTU and the power cabinet through the maintenance bench power duct and an external power cable.

## TM 9-1430-655-20-5-2

Figure 5-1. MTU Major Subassemblies.

MS 197058

MS 197066

Figure 5-2. MTU Component Location.

b. Magnetic Tape Transport AI and Cartridge (fig. 5-1). The magnetic tape transport (MTT) is a selfcontained tape transport unit consisting basically of the tape-movement mechanism, read/ write/erase tape heads, motor control circuit card, read/write circuit card, and control logic circuit cards. The MTT is installed in the MTU through the front-panel assembly and is secured to the front panel by six captive screws. Connectors JI and J2 are provided at the rear of the MTT for power and signal interface with MTU connectors W2P4 and W3P2, respectively (fig. 5-2). These connectors are accessible from the left side of the MTU when the slide-mounted frame is extended from the maintenance bench. The magnetic tape cartridge is installed and removed from the MTT through the spring-loaded access door on the front panel. Front panel controls and indicators are also accessible when the access door is in the open position. The tape cartridge consists of a tape supply and take-up reel, magnetic tape, and a tapetension mechanism. А write/protect cam is located on the front of the cartridge to prevent inadvertent destruction of recorded data.

*c.* Card Cage Assembly A2 (fig. 5-1). Included in card cage assembly A2 are two card shelves on a common wirewrap plane, with each shelf containing 32 digital circuit cards. The card cage and other MTU subassemblies are interconnected through ribbon-type cables W2 and W3 (fig. 5-2), the connectors of which connect to assigned card slots. Card cage assembly A2 is accessible from the right side of the MTU when the slide-mounted frame is extended from the maintenance bench.

*d.* DC/DC Converter PS1 (fig. 5-1). Dc/dc converter PS1 is installed in the upper-rear corner of the frame assembly and is secured with four mounting screws that are accessible from the right side of the MTU. Connectors J 1 and J2 are provided at the rear of the dc/dc converter for interface with MTU connectors W2P3 and WIPI, respectively (fig. 5-2). These connectors are accessible from the left side of the MTU when the slide-mounted frame is extended from the maintenance bench.

*e. MTU Cabling.* Figure 5-3 provides an overall cabling diagram for the MTU and illustrates the internal

interconnection of wiring harnesses and cable assemblies contained in the MTU.

*f: Circuit Card Location.* Positions for circuit card assemblies within card cage assembly A2 are shown in figure 5-2. The MTU circuit card complement and locations are specified in TM 9-1430-65520-5.

**5-5.** Circuit Card Location Index Tables and Key Signal Lookup Tables. Circuit card location index tables and key signal lookup tables provide figure references to functional logic diagrams. They permit rapid location of circuit areas corresponding to circuit card locations or signal mnemonics.

a. Card Location in Index. Table 5-1 shows the circuit card slots for the subassemblies of the MTU. This table provides figure and sheet references to the logic diagrams for specific circuit cards. Since often a card is used for various functional applications, certain cards have several figure references. The card location in logic diagrams index also indicates if a card can be tested by the MTS.

b. Key Signal Lookup. Table 5-2 lists the key signal lookup for the subassemblies of the MTU. Key signals are interconnecting signals going between physical assemblies or functional circuit areas as defined by the logic diagrams. Key signals are listed in alphanumerically order. The columns under the distribution heading list the foldout numbers and sheet number of each occurrence of the signal and the associated connector and pin number at which the signal is located on the foldout. They appear as follows:

1100 121041

The first number is the foldout number (foldouts are located in volume 3). The first two digits are the foldout number and the last two digits are the sheet number. On a foldout with only one sheet, the last two digits are zeros. The second number is the connector and pin. Without a letter prefix, this is a card connector. An A prefix indicates an assembly connector, an X prefix indicates a socket, and a W prefix indicates a cable connector. An asterisk (\*) before the connector indicates the source of the signal.

MS 197095

Figure 5-3. MTU Cabling Diagram.

| Card Slot |      | FO Sheet |      |  |

|-----------|------|----------|------|--|

| 1101      | 0301 | 0302     | 0800 |  |

|           | 1201 | 1802     | 2000 |  |

|           | 2501 | 2502     |      |  |

| 1102      | 0301 | 0302     | 1002 |  |

|           | 1202 | 1802     | 1900 |  |

|           | 2000 | 2501     | 2502 |  |

|           | 2700 |          |      |  |

| 1104      | 0100 | 0302     | 1202 |  |

|           | 2102 | 2502     | 2700 |  |

| 1105      | 0301 | 0302     | 0800 |  |

|           | 1002 | 1202     | 1802 |  |

|           | 1900 | 2000     | 2501 |  |

| 1106      | 0301 | 2700     |      |  |

| 1107      | 0301 |          |      |  |

| 1108      | 0302 |          |      |  |

| 1109      | 0302 |          |      |  |

| 1110      | 0302 |          |      |  |

| 1111      | 0302 |          |      |  |

| 1112      | 0301 | 2700     |      |  |

| 1113      | 0301 | 0302     | 0500 |  |

|           | 1002 | 1202     | 1802 |  |

|           | 1900 | 2000     |      |  |

| 1114      | 0301 | 0302     | 1002 |  |

|           | 1202 | 1802     | 1900 |  |

|           | 2000 |          |      |  |

Table 5-1. Card Location in Logic Diagrams Index

|           |      | - •      |      |  |

|-----------|------|----------|------|--|

| Card Slot |      | FO Sheet |      |  |

| 1115      | 0100 | 0301     | 0800 |  |

|           | 0901 | 1202     | 1700 |  |

|           | 1802 | 2000     | 2700 |  |

| 1116      | 0301 | 0302     | 0500 |  |

|           | 0600 | 0800     | 0901 |  |

|           | 0902 | 1700     |      |  |

| 1117      | 0600 | 0700     | 0901 |  |

|           | 0902 | 1700     | 2000 |  |

| 1118      | 0600 | 0700     | 0901 |  |

|           | 1700 | 2000     |      |  |

| 1119      | 0600 | 0700     | 0901 |  |

|           | 0902 | 1700     | 2000 |  |

| 1120      | 0100 |          |      |  |

| 1121      | 0302 | 0500     | 0600 |  |

| 1122      | 0301 | 0302     | 0600 |  |

| 1123      | 0500 |          |      |  |

| 1124      | 1201 | 1202     | 1400 |  |

|           | 1600 | 1700     | 1801 |  |

|           | 1802 |          |      |  |

| 1125      | 0400 | 1001     | 1201 |  |

|           | 1802 |          |      |  |

| 1126      | 1201 | 1400     | 1500 |  |

|           | 1600 | 1801     | 1802 |  |

| 1127      | 0400 | 1201     | 1202 |  |

|           | 1300 | 1500     | 1600 |  |

|           |      |          |      |  |

Table 5-1. Card Location in Logic Diagrams Index - Continued

| Card Slot |      | FO Sheet |      |

|-----------|------|----------|------|

|           | 1801 | 1802     |      |

| 1128      | 0400 | 0600     | 0800 |

|           | 1500 |          |      |

| 1129      | 0400 | 0800     | 1500 |

| 1130      | 0400 | 1001     | 1201 |

|           | 1202 | 1400     | 1500 |

|           | 1600 | 1801     |      |

| 1131      | 1400 | 1500     | 1801 |

| 1132      | 1300 | 1400     | 1500 |

| 1133      | 0400 | 1001     | 1002 |

|           | 1100 | 1201     | 1202 |

|           | 1300 | 1400     | 1500 |

|           | 1801 | 1900     | 2101 |

|           | 2700 |          |      |

| 1134      | 1201 | 1202     | 1400 |

|           | 1500 | 1600     | 1801 |

|           | 2102 |          |      |

| 1135      | 0100 | 1001     | 1201 |

|           | 1300 | 1802     | 1900 |

|           | 2000 | 2101     | 2102 |

|           | 2700 |          |      |

| 1136      | 1001 | 1002     | 1201 |

|           | 1202 | 1300     | 1400 |

|           | 1900 | 2101     | 2102 |

|           | 2700 |          |      |

| 1202      | 0200 | 0600     | 1100 |

|           |      |          |      |

Table 5-1. Card Location in Logic Diagrams Index - Continued

| Card Slot |      | FO Sheet |      |   |

|-----------|------|----------|------|---|

|           | 1201 | 1400     |      | _ |

| 1203      | 0200 | 0600     | 1100 |   |

|           | 1201 | 1400     |      |   |

| 1204      | 0200 | 0600     | 1100 |   |

|           | 1201 | 1400     |      |   |

| 1205      | 0200 | 0600     | 1100 |   |

|           | 1201 | 1400     |      |   |

| 1206      | 0100 | 0200     | 0600 |   |

|           | 1100 | 1201     | 1400 |   |

| 1207      | 0100 | 0500     | 0600 |   |

|           | 1802 |          |      |   |

| 1208      | 0100 | 0200     | 0500 |   |

|           | 0600 | 0800     | 0901 |   |

|           | 1001 | 1700     | 1802 |   |

|           | 2000 |          |      |   |

| 1209      | 0100 | 0200     | 0500 |   |

|           | 0600 | 0800     | 0901 |   |

|           | 1700 | 1802     | 2000 |   |

| 1210      | 0200 | 0700     | 1100 |   |

| 1211      | 0200 | 0301     | 0500 |   |

|           | 1100 |          |      |   |

| 1212      | 0200 | 0302     | 0800 |   |

|           | 1100 |          |      |   |

| 1213      | 0301 | 0600     | 0800 |   |

|           | 0901 | 1001     | 1100 |   |

|           | 1700 | 1802     | 2000 |   |

|           |      |          |      |   |

Table 5-1. Card Location in Logic Diagrams Index - Continued

| Card Slot |       | FO Sheet |      |  |

|-----------|-------|----------|------|--|

| 1214      | 0301  | 0600     | 0700 |  |

|           | 0800  | 0901     | 1001 |  |

|           | 1002  | 1201     | 1802 |  |

|           | 2000  |          |      |  |

| 1215      | 0800  | 6901     | 0902 |  |

|           | 1001  | 1700     |      |  |

| 1216      | 0800  | 0901     | 0902 |  |

|           | 1 802 |          |      |  |

| 1217      | 0600  | 0700     | 0901 |  |

|           | 1001  | 1002     | 1600 |  |

|           | 1802  |          |      |  |

| 1218      | 0600  | 0800     | 0901 |  |

|           | 0902  | 1001     |      |  |

| 1220      | 1001  | 1002     |      |  |

| 1221      | 0901  | 1001     | 1002 |  |

|           | 1201  | 1802     | 2000 |  |

| 1222      | 0302  | 1001     | 1002 |  |

|           | 1201  | 1400     | 1900 |  |

|           | 2000  |          |      |  |

| 1223      | 0500  | 1001     | 1002 |  |

|           | 1201  | 1700     | 1900 |  |

|           | 2000  |          |      |  |

| 1224      | 0500  | 0700     | 1001 |  |

|           | 1002  | 1202     | 1802 |  |

|           | 2000  |          |      |  |

| 1225      | 0500  | 1001     | 1002 |  |

|           |       |          |      |  |

Table 5-1. Card Location in Logic Diagrams Index - Continued

| Card Slot |      | FO Sheet | t    |

|-----------|------|----------|------|

|           | 1202 | 1600     |      |

|           | 1802 | 2000     |      |

| 1226      | 1001 | 1201     | 1202 |

|           | 1600 | 1801     |      |

| 1227      | 1001 | 1002     | 1202 |

|           | 1600 | 1900     | 2000 |

| 1228      | 0302 | 1001     | 1002 |

|           | 1201 | 1202     | 1400 |

|           | 1600 | 1900     |      |

| 1229      | 0901 | 1001     | 1201 |

|           | 1202 | 1400     | 1600 |

|           | 1900 | 2000     |      |

| 1230      | 1001 | 1201     | 1400 |

|           | 1600 | 1801     |      |

| 1231      | 1201 | 1202     | 1400 |

|           | 1500 | 1900     |      |

| 1232      | 1201 | 1400     |      |

| 1233      | 1500 | 1801     |      |

|           | 1812 | 0600     |      |

Table 5-1. Card Location in Logic Diagrams Index - Continued

| Signal  |      |           |      | Distribution |      |           |

|---------|------|-----------|------|--------------|------|-----------|

| DEVIN1  | 0302 | 1102-13   | 0302 | 1104-13      | 2502 | 1102-13   |

|         | 2502 | *PS1J1-14 | 2502 | W2PI-13      | 2502 | W2P3-14   |

|         | 2700 | 1102-13   | 2700 | 1104-13      |      |           |

| DEVINH  | 0302 | *1104-14  | 0302 | 1121-05      | 0302 | 1121-10   |

|         | 0302 | 1121-13   | 0302 | 1121-18      | 0302 | 1121-25   |

|         | 0302 | 1121-26   | 0302 | 1121-34      | 0302 | 1121-42   |

|         | 0302 | 1121-56   | 0600 | 1121-37      | 0600 | 1213-49   |

|         | 0700 | 1224-10   | 2700 | 1104-14      |      |           |

| LOGOR1  | 2502 | 1102-39   | 2502 | 1104-40      | 2502 | *PS1J1-16 |

|         | 2502 | W2P1-39   | 2502 | W2P3-16      | 2700 | 1102-39   |

|         | 2700 | 1104-40   |      |              |      |           |

| MTSGR   | 2700 | 1104-01   | 2700 | 1104-02      | 2700 | 1104-03   |

|         | 2700 | *1104-04  |      |              |      |           |

| SENVL1  | 2700 | 1104-45   | 2700 | *1106-28     |      |           |

| SENVL2  | 2700 | 1104-39   | 2700 | 1104-43      | 2700 | 1104-65   |

|         | 2700 | *1112-24  |      |              |      |           |

| T003MA  | 0200 | *1208-38  | 0200 | 1210-15      |      |           |

| Т003МО  | 0200 | *1210-10  | 1600 | 1127-68      |      |           |

| T005MA  | 0200 | *1208-30  | 0200 | 1210-21      |      |           |

| T005MO  | 0200 | *1210-19  | 1001 | 1224-03      |      |           |

| TO1 2MA | 0200 | 1210-27   | 0200 | *1211-23     |      |           |

| T015MA  | 0200 | 1210-38   | 0200 | *1211-33     |      |           |

| T01 8SA | 0200 | 1210-47   | 0200 | *1211-45     |      |           |

| T01 8S0 | 0200 | *1210-49  | 1802 | 1225-72      |      |           |

| T020MA  | 0200 | *1208-33  | 0200 | 1210-35      |      |           |

Table 5-2. Key Signal Lookup Listing - Continued

| Signal  |      |          |      | Distribution |      |         |  |

|---------|------|----------|------|--------------|------|---------|--|

| T020M0  | 0200 | *1210-37 | 1600 | 1225-68      |      |         |  |

| T023MA  | 0200 | 1210-36  | 0200 | *1211-21     | 1600 | 1126-77 |  |

| T040M0  | 0200 | *1210-34 | 1001 | 1217-19      | 1001 | 1220-49 |  |

|         | 1001 | 1220-62  |      |              |      |         |  |

| T047UA  | 1100 | 1133-74  | 1100 | *1211-57     |      |         |  |

| T047UO  | 1100 | *1133-72 | 1201 | 1232-08      | 1202 | 1134-36 |  |

| T048UA  | 1100 | 1210-50  | 1100 | *1211-69     |      |         |  |

| T048UO  | 1100 | *1210-48 | 1202 | 1229-35      |      |         |  |

| TO4MHJ  | 0100 | *1120-33 | 0100 | 1206-60      | 0100 | 1207-60 |  |

| T050MA  | 0200 | *1208-52 | 0200 | 1210-29      |      |         |  |

| T050MO  | 0200 | *1210-30 | 1002 | 1225-54      |      |         |  |

| T060MA  | 0200 | *1208-46 | 0200 | 1210-33      |      |         |  |

| T075MO  | 0200 | *1210-40 | 1201 | 1226-19      |      |         |  |

| T075UA  | 0200 | 1210-09  | 0200 | *1211-35     |      |         |  |

| T075UO  | 0200 | *1210-07 | 1600 | 1226-73      |      |         |  |

| T080MO  | 0200 | *1210-31 | 0901 | 1221-25      | 1001 | 1221-19 |  |

|         | 1201 | 1127-11  |      |              |      |         |  |

| T150MA  | 0200 | 1210-39  | 0200 | *1211-47     |      |         |  |

| T1 50MO | 0200 | *1210-42 | 1001 | 1221-73      | 1802 | 1225-79 |  |

| T16MHA  | 0100 | 1120-47  | 0100 | *1120-48     | 0100 | 1120-60 |  |

| T16MHO  | 0100 | *1120-51 | 0600 | 1117-70      | 0600 | 1118-70 |  |

|         | 0600 | 1119-70  | 0700 | 1118-72      | 0700 | 1118-79 |  |

|         | 0700 | 1119-72  | 0700 | 1119-79      |      |         |  |

| T16MIO  | 0100 | *1120-54 | 0600 | 1202-10      | 0600 | 1203-10 |  |

|         | 0600 | 1204-10  | 0600 | 1205-10      | 0600 | 1206-10 |  |

|         | 2000 | 1227-05  |      |              |      |         |  |

Table 5-2. Key Signal Lookup Listing - Continued

| Signal  |      |          |      | Distribution |      |          |  |

|---------|------|----------|------|--------------|------|----------|--|

|         | 4400 | 4040.44  | 4400 |              |      |          |  |

| T390UA  | 1100 | 1210-41  | 1100 | *1211-76     |      |          |  |

| T390U0  | 1100 | *1210-46 | 1201 | 1225-47      |      |          |  |

| T4549A  | 1100 | 1133-69  | 1100 | *1211-59     |      |          |  |

| T45490  | 1100 | *1133-70 | 1202 | 1134-03      | 1202 | 1134-04  |  |

|         | 1202 | 1134-08  | 1202 | 1134-11      | 1202 | 1134-17  |  |

|         | 1202 | 1134-18  | 1202 | 1134-23      | 1202 | 1134-24  |  |

|         | 1202 | 1134-40  |      |              |      |          |  |

| T900MA  | 0200 | *1208-45 | 0200 | 1210-52      |      |          |  |

| TADS1AR | 2102 | *1136-43 | 2102 | A10A1-J1     | 2102 | A1J2-71  |  |

|         | 2102 | W3P1-43  | 2102 | W3P2-71      | 2102 | XA4-21   |  |

|         | 2700 | W3P1-43  | 2700 | W3P1-44      | 2700 | W3P2-71  |  |

|         | 2700 | W3P2-72  |      |              |      |          |  |

| TBKK1A  | 1700 | 1208-23  | 1700 | *1213-50     |      |          |  |

| ΤΒΟΤΟΑ  | 1900 | *1222-39 | 1900 | 1228-74      |      |          |  |

| TBOTOR  | 1001 | 1221-72  | 1400 | 1230-19      | 1900 | *1227-69 |  |

|         | 1900 | 1227-69  | 1900 | 1228-65      |      |          |  |

| TBOTOS  | 0500 | 1123-35  | 0500 | 1123-53      | 1001 | 1222-41  |  |

|         | 1001 | 1223-13  | 1900 | 1113-68      | 1900 | 1227-65  |  |

|         | 1900 | 1227-78  | 1900 | *1228-69     | 1900 | 1228-69  |  |

|         | 1900 | 1229-62  | 1900 | 1229-75      |      |          |  |

| TBOT1 A | 1900 | 1227-74  | 1900 | *1231-76     |      |          |  |

| TBOT1R  | 1900 | 1228-59  | 1900 | *1229-55     | 1900 | 1231-78  |  |

| TBOT1S  | 1001 | 1213-65  | 1900 | 1227-29      | 1900 | *1228-63 |  |

|         | 1900 | 1228-63  | 1900 | 1229-53      |      |          |  |

| TBOT2A  | 1900 | 1228-61  | 1900 | *1229-73     |      |          |  |

| TBOT2R  | 1900 | *1227-80 | 1900 | 1228-76      | 1900 | 1229-77  |  |

|         | 1000 | 1227 00  | 1000 | 1220 70      | 1000 | 1220 11  |  |

Table 5-2. Key Signal Lookup Listing - Continued

| Signal  |      |          |      | Distribution |      |          |  |

|---------|------|----------|------|--------------|------|----------|--|

| TBOT2S  | 1900 | 1223-59  | 1900 | 1227-76      | 1900 | *1228-80 |  |

| ТВОТЗА  | 1900 | *1222-63 | 1900 | 1229-60      |      |          |  |

| TBOT4A  | 1900 | *1227-33 | 1900 | 1228-78      |      |          |  |

| твотсо  | 1002 | 1222-49  | 1900 | *1133-63     | 1900 | 1133-63  |  |

|         | 1900 | 1222-35  |      |              |      |          |  |

| ΤΒΟΤΙΒ  | 1900 | 1102-75  | 1900 | 1105-65      | 1900 | *1113-66 |  |

|         | 1900 | *1114-66 | 1900 | W2DS2-02     | 1900 | W2P1-75  |  |

|         | 2501 | 1102-75  | 2501 | W2DS-02      | 2501 | W2P1-75  |  |

| TBOTIBR | 0301 | 1102-76  | 0301 | 1106-32      | 2501 | 1102-76  |  |

|         | 2501 | W2P1-76  | 2501 | *W2S6-06     |      |          |  |

| TBOTID  | 1900 | 1105-65  | 1900 | *1113-66     |      |          |  |

| TBOTJD  | 1900 | 1105-65  | 1900 | *1114-66     |      |          |  |

| TBSYOA  | 1001 | *1220-23 | 1001 | 1222-07      | 1001 | 1228-13  |  |

| TBSY1A  | 1001 | 1220-20  | 1001 | *1223-09     |      |          |  |

| TBSY2A  | 1001 | 1220-22  | 1001 | *1223-15     |      |          |  |

| TBUSYR  | 0901 | 1215-26  | 0901 | 1218-10      | 1001 | 1213-59  |  |

|         | 1001 | *1221-11 | 1001 | 1222-03      | 1001 | 1230-73  |  |

| TBUSYS  | 1001 | 1221-06  | 1001 | 1221-49      | 1001 | 1221-77  |  |

|         | 1001 | *1222-09 | 1001 | 1224-70      | 1002 | 1220-31  |  |

|         | 1002 | 1224-56  |      |              |      |          |  |

| TCOOBP  | 0200 | *1202-21 | 0200 | 1211-40      |      |          |  |

| TCOOBQ  | 0200 | *1202-19 | 0200 | 1203-18      | 0200 | 1212-43  |  |

| TC01BQ  | 0200 | *1203-19 | 0200 | 1204-18      |      |          |  |

| TC02BQ  | 0200 | *1204-19 | 0200 | 1205-18      |      |          |  |

| TC03BQ  | 0200 | *1205-19 | 0200 | 1206-18      |      |          |  |

| TC04BP  | 0200 | 1202-18  | 0200 | *1206-21     | 0200 | 1210-65  |  |

|         |      |          |      |              |      |          |  |

Table 5-2. Key Signal Lookup Listing - Continued

|      |                                                             |                                                                                                                                                                                                                                                                                                                                                                                               | Distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                       |

|------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| 0200 | 1211-42                                                     |                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                       |

| 0200 | *1206-19                                                    | 0200                                                                                                                                                                                                                                                                                                                                                                                          | 1212-46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                       |

| 0200 | *1202-37                                                    | 0200                                                                                                                                                                                                                                                                                                                                                                                          | 1203-40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1212-48                                               |

| 0200 | *1203-37                                                    | 0200                                                                                                                                                                                                                                                                                                                                                                                          | 1204-40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1211-37                                               |

| 0200 | *1204-35                                                    | 0200                                                                                                                                                                                                                                                                                                                                                                                          | 1211-38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                       |

| 0200 | *1204-37                                                    | 0200                                                                                                                                                                                                                                                                                                                                                                                          | 1205-40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                       |

| 0200 | *1205-37                                                    | 0200                                                                                                                                                                                                                                                                                                                                                                                          | 1206-40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                       |

| 0200 | 1202-40                                                     | 0200                                                                                                                                                                                                                                                                                                                                                                                          | *1206-35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1210-79                                               |

| 0200 | *1206-37                                                    | 0200                                                                                                                                                                                                                                                                                                                                                                                          | 1212-49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                       |

| 0200 | *1202-31                                                    | 0200                                                                                                                                                                                                                                                                                                                                                                                          | 1203-34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1212-50                                               |

| 0200 | *1203-31                                                    | 0200                                                                                                                                                                                                                                                                                                                                                                                          | 1204-34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                       |

| 0200 | *1204-31                                                    | 0200                                                                                                                                                                                                                                                                                                                                                                                          | 1205-34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                       |

| 0200 | *1205-31                                                    | 0200                                                                                                                                                                                                                                                                                                                                                                                          | 1206-34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                       |